Off The Top

Work in Progress, Planning, Future Attractions

Off The Top Description

Off The Top; is a forum to present products, concepts, techniques, and strategies for implementing your system with information about current work, past accomplishments, and future plans. Use our On Deck products for your proposals - they will be Mission Accomplished when your PO comes in.

We continuously build our business with our satisfied customers. We appreciate your referrals. At Dynamic Engineering we are open to your suggestions and specific requirements. Perhaps you have an idea for a new product, or how to make an existing product better for you. Send your dynamic ideas to engineering@dyneng.com. Let us know who you are referring and what your ideas are... and we would like to send you a thank you gift.

White Papers

-

Monitor/Debugger for Spacewire White paper and product selection for low cost rapid deploy portable spacewire monitor and debugger. Provides nearly instantaneous around the world portable SpaceWire solution. Download the full Spacewire_WhitePaper presented at the 2008 International Spacewire Conference.

-

Dynamic Engineering Designs for Optimal Client Use Read about Dynamic Engineering power consumption design process.

PMC-MC-X2 and PMC-MC-X4 are usually supplied with a T1042 processor. The following papers will help you to minimize your integration time. The first paper deals with the "tool chain" used to develop your application on a PC and to cross compile onto the PrPMC-T1042 target.

-

How to prepare your PC for P2020 development This white paper addresses the SW needed, how to install and set-up for successful application development and cross compilation to the P2020 target.

On Deck

prPMC-T1042Current status is: In development - Initializing with code warrior. Working our way down the list.

Current status is: Production. Windows software package included with purchase. Reference User FPGA design available.

Current status is: In Layout Queue

Current status is: In Layout. Secondary design to convert from PCIe to cPCIe is on-deck to support development with this device.

ccPMC-SpaceWire

PCIe8LXMCX2

PMC Mini Chassis X2 and motherboard

PMC Mini Chassis X4 and motherboard

Future Attractions

Products that are planned

Dynamic Engineering frequently helps with customer architecture and design solutions. Call and we can help you.

Please share your requirements with us - format, functions, special features required, method of cooling, temperature range etc.engineering@dyneng.com or 831.457.8891

PCIe is becoming main stream, and Dynamic Engineering has support with carriers and native cards. Please look under Embedded Products => PCI Express for a complete list including:PCIeBPMCX1 adapter for PMC into a PCIe slot, PCIeBPMCX2 - two postion version, PCIe8LXMCX1 , PCIe8LXMCX2 - PCIe adapters for XMC , PCIe adapters for IndustryPack® [PCIe3IP, PCIe5IP], SpaceWire and others. See above for features and status.

PCIe carriers for cPCIe - Adapter to allow installation of 3U cPCIe board in PCIe slot. 8 lanes, local 5V, 3.3V supplies, IO routed from XP2/XJ2 to SCSI connector at Bezel.

IP and PMC carriers for VPX - [VPX2IP Released] VPX4IP, VPXBPMCX1, VPXBPMCX2 similar to the current PCIe and cPCI based models.

IP carriers for PCIe - versions for VPX, PC104 Express, cPCI Express planned. PCIe3IP, PCIe5IP , VPX2IP Designs completed. See above for more details.

XMC carriers for VPX and cPCIe 3U and 6U 4HP - Industrial Temp, Zero Slot Fan supported, Local Power supplies. VPX8LXMC3U design completed.

PMC-429 with flow through data architecture to allow programmed transmission of data, and data filtering functions to be added.

PMC-Parallel-HV - Up to 40V operation, with programmable input thresholds - COS on all inputs, memory and DMA for waveform applications, clocking options.

PMC-OptoISO - Up to 60V operation, with optical Isolation. 1.5A on each channel. Matching OptoIso inputs.

PMC-XM-TTL => update the PMC-XM to have TTL IO and connector built in

PCI-104-User-Diff => Port of the PMC version to PCI-104.

cPCI 3U, VME 3U, VPX 3U

Dynamic Engineering frequently helps with customer architecture and design solutions. Call and we can help you.

Please share your requirements with us - format, functions, special features required, method of cooling, temperature range etc.engineering@dyneng.com or 831.457.8891

CoolFan board to promote airflow. The Fan Board can make an effective method for spot cooling for high powered boards in tight places.

Zero slotfans available. 6U versions are available:cPCI-6U-COOL, VPX-6U-COOL and VME-6U-COOL

Mission Accomplished

Links to designs recently completed

Archive of previously completed projects

The Dynamic Data Sheets are useful for your immediate needs

PMC-BiSerial-VI - Designs Ported to PMC-BiSerial VI . Multiple designs ported to PMC-BiSerial-VI from previous BiSerial implementations. Win10 and Linux support currently. See UART, S311, OSEH, and HW1 versions released to date.

PMC BiSerial III Octal UART : 8 UARTs with RS422 at 5MHz - Design complete - tested at 10 MHz Full DMA support

PMC-SpaceWire has been updated [VHDL] to use the two external 128K x 32 FIFO´s on separate channels. Channel 0 and channel 1 will have larger receive side FIFO´s. Please note that our common FLASH model will allow this update to be offered on all models [PMC, ccPMC, PCI, and PC104p].

PMC-BiSerial-III has a new version "NG8" to handle Camera Data. Transmit or Receive with two channels per card. 133Kx32 FIFO to support either RX or TX function per channel. "Channelized DMA"™. PLL control of transmit frequency. HREF, VREF, Bad Pixel, Clock, Pixel Data [11:0]. Image size is programmable. Active and blanking areas are programmable. WIndows® driver available along with reference application. Hardware and Driver manuals on the BiSerial page

PCIBPMCET is a new design based on the PCIBPMC incorporating an industrial temperature bridge, and matched length differential routing to rear IO connectors. Offered with ROHS and standard processing. Please see the DDS for more information.

PMC-BiSerial-III has a new version to handle telemetry data "NASA1". 4 channels with 4 full duplex functions. LADEE - LLST, NMS, UART, Manchester [Uplink and Downlink]. "Channelized DMA"™. PLL control of transmit frequency. WIndows® driver available along with reference application. Hardware and Driver manuals on the BiSerial page

PCIeBiSerialDb37 is a PCIexpress format, half length design featuring a Spartan III FPGA with differential IO and a DB37 connector at the bezel. The 18 IO can be set to LVDS, RS-422/RS-485 or a combination. Full and half duplex operation, programmable direction and termination, FPGA and memory options, ROHS and standard processing, Windows® and Linux drivers. Initial implementation provides an ARC-210 compatible interface.

IP-Connector-Saver Necessity is the root of invention. Tired of wearing out our IP Module connectors during test we decided to design a connector saver for IP Modules. Combined Carrier side and Module side connectors in a stacked configuration using a miniature PCB allows us to test our Carriers without destroying our IP-Test modules. The added air-space between the IP and carrier can be used for increased air-flow and taller components. Since the full added space can go to the Module the effect is "triple" the IP component height that can be used.

PC104pPWR28. PC104p, PCI-104, PC104 compliant power supply with &34;28V&24; input power. All power rails energized [+12, -12, +5, +3.3, -5]. Headers available for chassis level fan support. VIO selection for PCI bus capable boards. Suitable for conduction and convertion cooled systems.

PCIBPC104pET is a PCI 1/2 length card featuring an "ET" bridge to support a PC104p stack in a PCI slot. 1-4 active modules can be in the stack. ROHS and standard processing available.

X2 Motherboard Updated design with enhanced power supplies, featuring 10A standard on 5V and 3.3V rails, 12 or 28V [14-40] power, improved regulation, built in slot 0 functions - arbitration, clock reference, reset, interrupt routing etc., and improved clock options : 33, 66, 100, 133

X4 Motherboard Updated design with enhanced power supplies, featuring 10A standard on 5V and 3.3V rails, 12 or 28V [14-40] power, improved regulation, built in slot 0 functions - arbitration, clock reference, reset, interrupt routing etc., optional fused power to header for embedded situations where coupled with external HW. Voltage monitor and over temperature power supply control. New option for vertical power connector.

Industrial printing application. Combination of base board with multiple power supplies, microprocessor, multiple FPGA's and other custom hardware and Interface cards which plug into base board. We are working closely with our client on this project. Our client had a prototype which "needed help" We have helped with system design, repackaging, redesigning, reducing and improving the design to allow for production and reliability. We are through the initial testing and a mini-production run. Currently in second level production. Client and exact application withheld by NDA

PCI-Altera design customization. Combined operation with 485 and TTL signals for a data transfer interface. Design will be used as a test aparatus for programming and testing a large block of memory. Agilent is the client.

PCI-ECL-II - recently completed new design with 20 ECL outputs, 20 ECL inputs, 12 TTL IO, plus 32 Mb SDRAM x2. Initial design is the STE3 - an updated version of STE1,2 with the larger memories.

PC104p-COOL Fan card designed to support PC104, PC104p, PCI-104 chassis level cooling. Zero SLot fans used to allow single module thickness.

PC104p-RPP Reverse Power Protection to support PC104, PC104p, PCI-104 chassis level power or for standalone use. FET based for very low "forward drop" losses. Offset entry and exit power connectors to align with the PC104pPWR supply cards. Can be used in non PC104 environments too

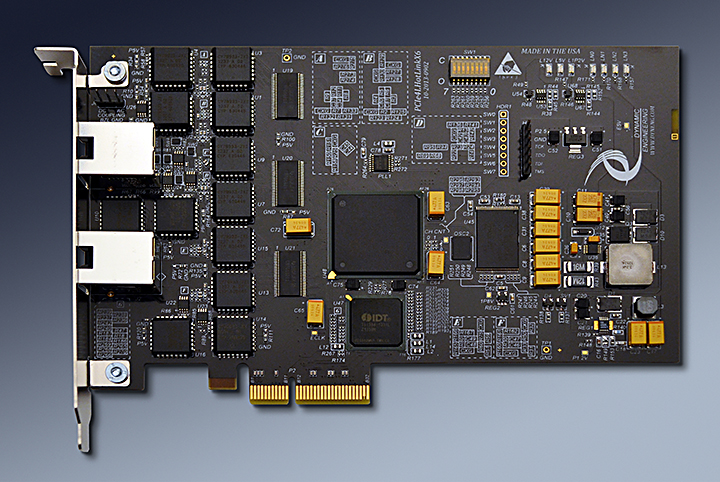

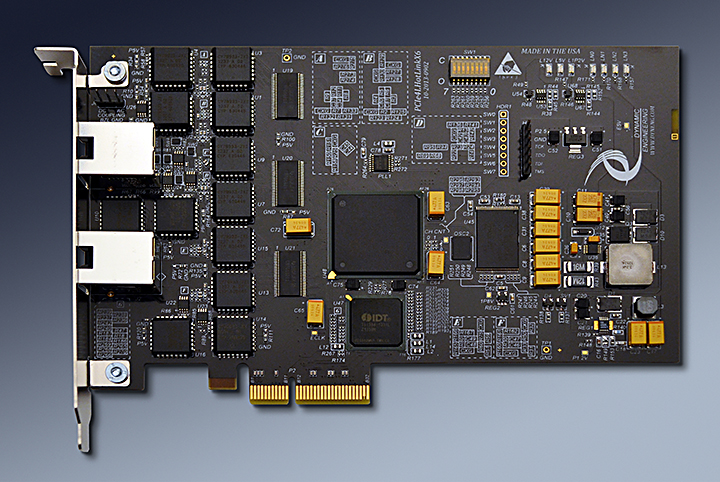

PCIeBPMCX2 Dual PMC carrier for PCIe. 4 lane interface, PCI/PCI-X supported, Pn4 [rear] IO and Bezel IO supported. 10A power supplies for 3.3 and 5V. -12V, +12V supported with 1A+ at each PMC. Zero slot Fan options.

IP-429-II 2-8 receivers, 1-4 transmitters, built in IO protection, 8/32 MHz IP interface, Windows® driver, Time Stamp on each Rx channel. 100 Mhz interface to 429 devices for minimized access delay. Interrupt and Polled support.

SpaceWire driver using INtime from Tenasys. The basic concept of the INtime system is to allow the real time component [SpaceWire in this case] run on a specified CPU in a multi-core system. This allows standard Windows to be operating on the other processors and the time critical function on the dedicated processor. Driver is completed. Client has completed their integration with success.

Update for the PMC-BiSerial-III to create the BAE9 version. Multiple 10 MHz UARTs with dual port RAM, retransmit capability, external triggering, periodic transmission and other custom features. Initial FLASH update delivered to client.

Update for the PMC-Parallel-485 to use a Spartan II FPGA instead of the original Spartan 40. Still a popular board and needed an update to replace hard to get parts and add features. SW compatible versions of the original implementations in progress. "NG1" completed. New versions by client request. Neew features include isolated IO from Bezel and Pn4, Spartan II, industrial temp components, 485 and or LVDS IO

Update for the PMC-XM-DIFF-60-MOD new version "Modbus" Multiple channels of Modbus and a client specific alternative are being incorporated. Design complete. Large design requiring a "60" size Virtex 4. Supported with VxWorks.

Update for the PMC-BiSerial-III-BAE9 Linux Driver and reference suite complete.

New Design VPX-Receiver Controller - VPX 3U 4 HP format, Special Purpose Receiver Interface support. Rear and Front panel IO. LVDS, 485, TTL IO types. Spartan 3 2000 for local FPGA with FLASH support. Production Status

Update for the PMC-Parallel-TTL to create an I2C IO "BA21" version. 4 channels with DMA support. Standard and "High Speed" supported with initial design.

Update for the PMC-BiSerial-III-HW2 Linux Driver and reference suite completed.

Client special motherboard to support hot swapping of "SSD" hard drives. 24 RAID drives plus 1 system. LED control, power distribution etc. Released to production.

cPCIRepeat32. cPCI 6U 4HP design with bridge to support non bridged motherboards. 32 bit PCI connection on J1, " Repeated PCI connection" on J2 with bus arbitration, interrupts, clock distribution and 32/33 3.3V PCI implementation. Motherboard routes J2 to J1 on up to 6 additional postions. Schematic complete. Layout complete. Tested with custom Motherboard, cPCI2PMC-SLT0, cPCI2PMC, and BA16. We will use a PrPMC mounted to the Slot0 cPCI2PMC, and run tests on the BA16 mounted to the second cPCI2PMC to exercise both sides of the cPCIRepeat32. Released to Manufacturing.

HotLINK based PCIe card with LVDS IO. 2 channels full duplex plus 4 channels 1/2 duplex. 1/2 size card with Spartan 6 based on PCIeBiserial3Db37 design. Schematic and Layout complete. Prototypes assembled. Successful sell-off with client. Initial version uses 4 1/2 duplex channels to receive high speed data from instrumentation. Win7 and Linux support available. Design updated to support PECL as well as LVDS. Second delivery with 6 channels to support additional requirements. Programmable framing sequences. PCIe4lHOTLinkx6 design complete

ccPMC-HotLINK has been updated to meet client requirements. Spartan 3 changed to Spartan 6. Updated power supplies, decoupling etc. Used for an image capture application. First implementation on new fab delivered to client. Win7 support.

PCIeBiSerialDb37-BA22 has been updated. The image data interface is now more programmable with the ability to handle various camera interface requirements. Specifically a programmable sequence for the frame synchonization pattern and idle control were added. In Client T&I.

PMC-BiSerial-III has a new version. 8 UART´ Packetized, Packed, Unpacked modes, 2 MHz. operation. RS-422 IO. New feature is a programmable delay for the Packetized mode. Completed

PCIeBiSerialDb37-L3COM1 has been added. An update to the RTN8 design with flwo control and half duplex operation. Programmable byte wide data path. Linux support. In Client T&I.

PCIe8LSwVPX3U is completed and in manufacturing status. Use your VPX card in a PC PCIe slot. Full access to both sides of the VPX card for development. This version has a switch to allow use of the VPX in a Spread Spectrum clock situation like your PC. 8 lanes available to the VPX, VPX power on P0 with local power supplies for the non PCIe standard voltages.

PMC-BiSerial-III has a new version. -SDLC has multiple SDLC channels with Differential IO. External or internal reference clock, local RAM with circular buffers, Win7 and Linux support.

PCI-ECL-II has a new Linux Driver completed for the STE3A model. STE3A features 8 bit parallel bidirectional [full duplex]data with reference clock and enable. DMA. 12 bit TTL port. Available now.

PCI-Altera has a new Win7 driver/UserAp . User Configurable logic with 40 LVDS/RS485 IO plus 12 TTL lines, 8 PLL´s, DMA support. XP, Linux, Win7. PCIeAlteraCycloneIV is recommended for new designs.

PMC-BiSerial-III has an updated Linux driver - updated for more recent Red Hat release. MDS1 version. 4 channels of manchester encoded serial data. 1/2 or full duplex. Dual Port RAM 512x32 for each channel.

PMC-OctalUART-232 (RS-232 interface, 8 UART´s with RX, TX, RTS, CTS, DTR, DSR ) was designed and tested to support one of our clients with a requirement for legacy HW. We matched the pinout of the original design and implemented a new version with sustainable components for the future. Currently supported with Win7 driver and application. Client had Linux software which only needed to be updated for the new CardId VendorId. Client tested on MVME1600 and MVME2400. Linux and VxWorks support planned.

PCIe5IP PCIe Carrier / Adapter for IndustryPack with 5 positions and individually selectable 8/32 operation. Win7, Linux, VxWorks support with IP-Generic included to allow for 3rd party IP modules to be used with PCIe5IP.

PCIe104DIFF-OS1 is finished with an LVDS based, serial interface including DMA support. Supported with Linux driver and application.

PCIe1LPCIe104 PCIe 1 lane card Carrier / Adapter for PCIe104. Test and Production positions with user selection. Gen1-3 compatible

PMC BiSerial VI Differential IO - LVDS and or RS485 - 34 pairs at the bezel / 32 pairs for rear IO applications. Spartan 6 -100 Industrial temp standard FPGA installed. Standard BiSerial family features: User Switch, 4 PLL´s, optional external FIFO´s, large array of pre-existing design work to pull from. Win7, Linux, VxWorks support

XMC-Parallel-TTL 64 independent TTL IO. Customizable FPGA with DMA. Front Panel and / or rear IO options . Win7, Linux, VxWorks support.

PMC-UNIV-TEST is a minimized passive interface to allow a PMC to be installed into a PCI position. Designed to provide access to the PMC main component area with a vertical rear mounted PMC orientation. Option for -ENG model adds the PMC side connectors to allow use in a PMC stack orientation. Testpoints on the PCI bus allow easy connection to the PCI bus with scope or logic analyzer in either model. SCSI connector with Pn4 IO for rear IO applications in the standard model

PCIe HOTLink New contract to develop a modified PCIe4lHOTLinkx6. The modified design has 4 ports on VHDCI and 1 port with coax style connectors. VHDCI ports have fiber support at the bezel. Win7 driver and application. Delivered.

HDEterm68 customized. New contract to develop a modified HDEterm68. The modified design will support Ethernet, Serial and parallel ports from rear IO [Pn4] of a PrPMC installed on the PMC-MC-X4 Rear IO model. HDEterm68-NG12 is the name of this model. Design also compatible with PMC-MC-X2-RIO Delivered

IP-BiSerial-VI-CTRB New contract to develop a modified IP-BiSerial-VI. The modified design add a counter timer function [8 channels] and is supported with Win7, Linux, and VxWorks. Internal and external clock options, programmable pulse generator coupled with timer. Delivered

IP-BiSerial-VI-SIB New contract to develop a modified IP-BiSerial-VI. The modified design has two channels each programmable to operate as one of two serial interface types. Supported with Win7, and Linux. Delivered.

PMC-BiSerial VI - New contract to develop a modified PMC-BiSerial VI . This is a major update to the PMC-BiSerial-III-UART adding DMA and special operating functions. Win7 driver and application completed. Linux in design. Initial units delivered

VPX-GLIB - New contract to develop a new VPX 3U card with multiple conversion processes to support CPU to System. Delivered

PMC-BiSerial VI - New contract to develop a modified PMC-BiSerial VI . This is a major update to the PMC-BiSerial-S311 adding a second port and updating to the new base design. Win7 driver and application in development. Also developed a Win7 SW package for the original PMC-BiSerial-S311 as part of this contract.

Contract to develop a modified ccPMC-HOTLink . Combination of TTL and HOTLink buses with Debian [Linux] support. RS485 devices were swapped out for TTL IO. TTL IO provides command traffic and HOTLink the data transfer. Shipped to client for integration. Delivered

IP-Parallel updated with new FPGA to allow for memory based IO functions, and enhanced base feature set. IP-Parallel-IO design updated to new FPGA.

ccPMC-BiSerial VI -ORN1- New implementation on ccPMC-BiSerial-VI platform ccPMC-BiSerial VI . This implementation features 2 SDLC ports and 2 NRZ(L) ports. The SDLC port is referenced to the PLL and external clock options. NRZ also has programmable frequency plus programmable bit length, MSB/LSB first operation, Data inversion. Remaining IO can be used for a parallel GPIO port. Unused SDLC or NRZL ports can be mapped out to expand the parallel port. Win10/11 plus Linux and VxWorks support packages.

Archive of previously completed projects

The Dynamic Data Sheets are useful for your immediate needs

Industrial printing application. Combination of base board with multiple power supplies, microprocessor, multiple FPGA's and other custom hardware and Interface cards which plug into base board. We are working closely with our client on this project. Our client had a prototype which "needed help" We have helped with system design, repackaging, redesigning, reducing and improving the design to allow for production and reliability. We are through the initial testing and a mini-production run. Currently in second level production. Client and exact application withheld by NDA

PCI-Altera design customization. Combined operation with 485 and TTL signals for a data transfer interface. Design will be used as a test aparatus for programming and testing a large block of memory. Agilent is the client.

PCI-ECL-II - recently completed new design with 20 ECL outputs, 20 ECL inputs, 12 TTL IO, plus 32 Mb SDRAM x2. Initial design is the STE3 - an updated version of STE1,2 with the larger memories.

PC104p-COOL Fan card designed to support PC104, PC104p, PCI-104 chassis level cooling. Zero SLot fans used to allow single module thickness.

PC104p-RPP Reverse Power Protection to support PC104, PC104p, PCI-104 chassis level power or for standalone use. FET based for very low "forward drop" losses. Offset entry and exit power connectors to align with the PC104pPWR supply cards. Can be used in non PC104 environments too

PCIeBPMCX2 Dual PMC carrier for PCIe. 4 lane interface, PCI/PCI-X supported, Pn4 [rear] IO and Bezel IO supported. 10A power supplies for 3.3 and 5V. -12V, +12V supported with 1A+ at each PMC. Zero slot Fan options.

IP-429-II 2-8 receivers, 1-4 transmitters, built in IO protection, 8/32 MHz IP interface, Windows® driver, Time Stamp on each Rx channel. 100 Mhz interface to 429 devices for minimized access delay. Interrupt and Polled support.

SpaceWire driver using INtime from Tenasys. The basic concept of the INtime system is to allow the real time component [SpaceWire in this case] run on a specified CPU in a multi-core system. This allows standard Windows to be operating on the other processors and the time critical function on the dedicated processor. Driver is completed. Client has completed their integration with success.

Update for the PMC-XM-DIFF-60-MOD new version "Modbus" Multiple channels of Modbus and a client specific alternative are being incorporated. Design complete. Large design requiring a "60" size Virtex 4. Supported with VxWorks.

Update for the PMC-BiSerial-III-BAE9 Linux Driver and reference suite complete.

Customized

Currently Dynamic Engineering has customized card designs under contract:

Just completed update of PMC-BiSerial-II-NG1 support package to update from XP to Win10. HW is almost 20 years old and still working in the field. PMC-BiSerial-VI is recommended for new designs.

Designing -SMB version of PCIe4LHOTLinkx5. Design is for Hadland Imaging to provide an updated interface for their ultra high speed camera designs. Preliminary VHDL and Win10 driver completed and in test. Based on the x6 standard implementation and tailored for a single port with SMB connectors.