ccPMC-BiSerial-VI

[conduction cooled] ccPMC Module with Spartan 6 FPGA, PLL, 32 Independent Differential IO - RS422, RS-485, LVDS

Order This Item

ccPMC-BiSerial-VI Description

- Windows, Linux

- Standard ccPMC module

- 32/33 with DMA operation

- 32 independent differential IO. Each with programmable termination and direction.

- RS-485, RS-422, LVDS and mixed

- Clock locked indicator

- Spartan 6 FPGA with BRAM for FIFO or RAM implementation

- DDR 256 MB

- PLL with 4 clock references

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature standard. -40C ⇔ +85C

- ROHS and Standard processing available

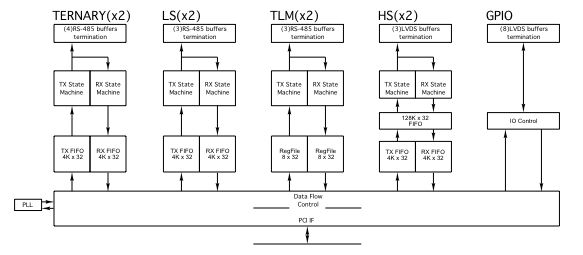

The PMC BiSerial family has been updated to include a Spartan 6 [Xilinx] based design with expanded capabilities. BiSerial-VI includes industrial temperature components, more internal RAM, DDR, clocks and gates for more complex designs. Building on the knowledge and experience gathered from multiple IP, PMC, and PCI-104 BiSerial implementations and adding in the latest technology has created ccPMC-BiSerial-VI. The advanced architecture provides multiple ports each with separate DMA controllers, wide data paths, and room for various IO implementations. DDR memory is available to provide mass storage for real time requirements or systems without flow control. The [32] RS-485 / LVDS buffers have individual programmable termination, and direction controls allowing for any combination of "In´s and Out´s". Half-Duplex, Full-Duplex and uni-directional systems can be configured with software and VHDL. The denser, faster FPGA will implement the most complex state-machines.

The IO can be configured to support one function, one function replicated several times, or multiple functions. A real space saver when you need to have some Manchester to go with your UART and HDLC ports. A partial list of functions implemented in "Channels" includes: NRZL, Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. To support the functions the designs include: memory elements instantiated with FIFO, Dual Port RAM, register files, as well as state-machines, counters, timers, dividers, registers, CRC and Parity generation / checking, software drivers and applications, DMA [direct memory access] and the glue that goes with it. Our designs are written in VHDL and done in a heirarchy allowing direct porting of different features to create new implementations.

More than 50 customerized versions of the BiSerial family and counting. ccPMC-BiSerial-VI as well as IP-BiSerial-VI, PMC-BiSerial-VI, PC104p-BiSerial-VI, PCIe-BiSerialDb37, and PMC-BiSerial-6T20 are recommended for new designs.

The hardware is used to interface with a wide variety of equipment. What do you need to communicate with? Control? Capture data from? Please see the bottom of this page and other BiSerial implementations for descriptions and manuals for our customerized versions. We have implemented custom versions of BiSerial since 1998 when IP-BiSerial was first released.

A new custom version can be implemented in a very reasonable time. Typically a few weeks of design time for a medium sized project including the new VHDL set, Windows® or Linux driver, reference software package, and documentation. Examples of the designs performed to date are listed toward the bottom of this page and pages for other versions of BiSerial.

We can be rapid with our response because the designs are structured to allow channels to be moved in and out to create new design sets. Most designs have a fairly large component of reused "known good" VHDL that we can pull from allowing us to focus on the new functions required for your implementation. You are getting the benefit of many man-years of design and test time with each new version created. Join our high reliability clients taking advantage of our know-how to help speed your project to completion.

ccPMC-BiSerial-VI can be used along with a PCIe or other carrier/adapter to use with a variety of system types - PCI, PCIe, PC104p, VPX cPCI, etc.. Dynamic Engineering has PMC carriers for PCI, PCIexpress, cPCI, PC104p, and can do custom design´s specific to client requirements as well. Please use the pull-down menu to navigate to other Dynamic Engineering products including carriers.

PMCs are independently specified through VITA for the form factor, connectors and pinouts of the PCI signaling; you can use the ccPMC-BiSerial-VI design with any carrier from any vendor that supports standard PMCs. To support integration into a variety of systems, ccPMC-BiSerial-VI features a universal PCI voltage design to allow operation with VIO set to 3.3 or 5V.

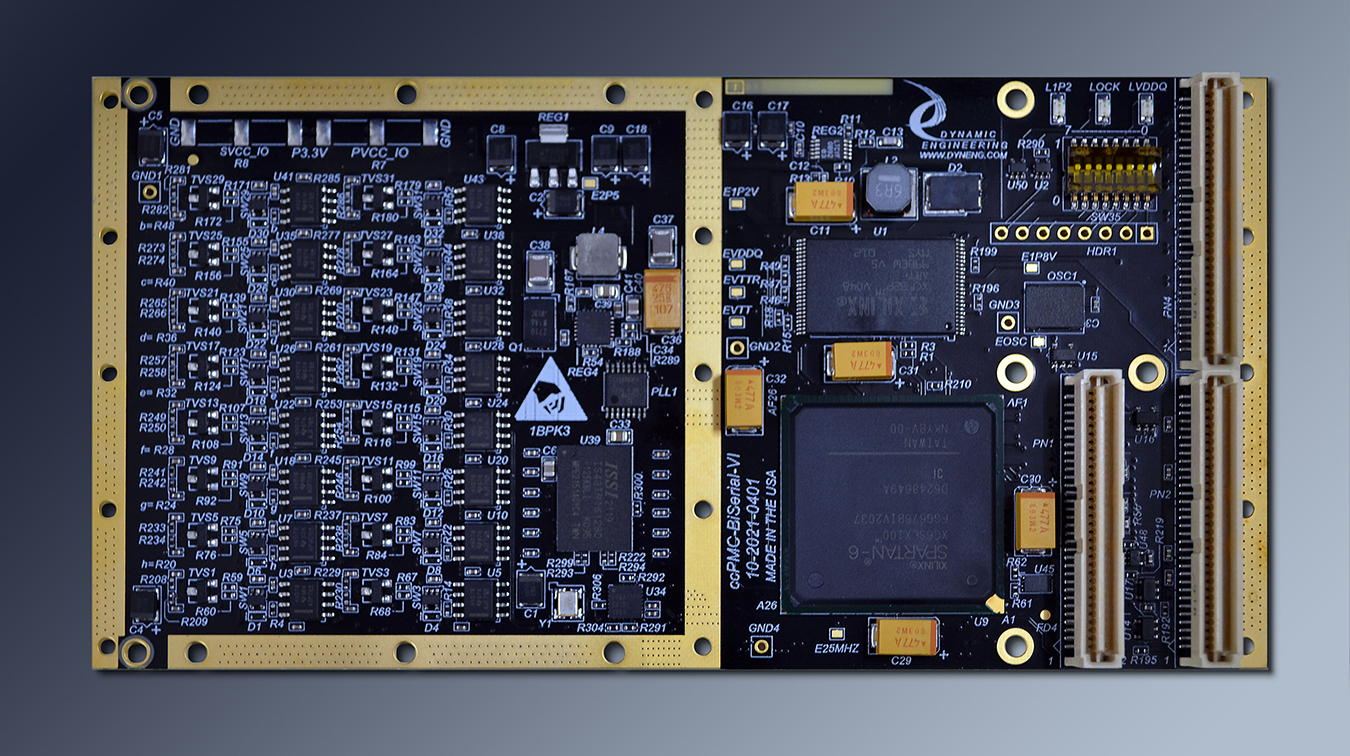

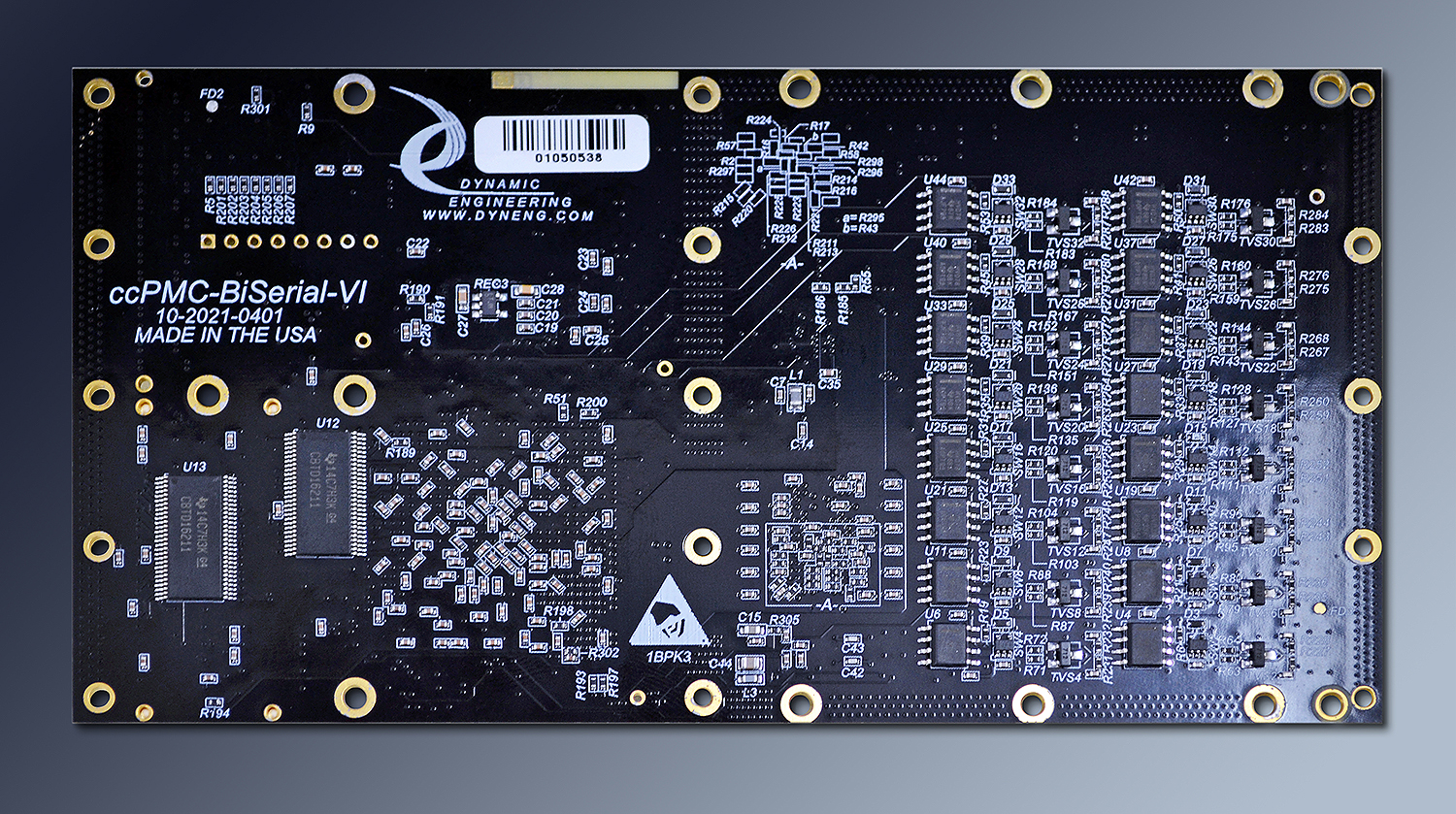

It all starts with the PCB [Printed Circuit Board]. Quality design and quality materials are required to meet the strenuous requirements of many of our implementations. You can do the job quickly or you can do the design correctly. We pride ourselves on taking the time to put the extra work into our layouts. The quality goes in before the parts go on. In addition to routing strategy and layer counts, Via size, plating requirements, break-out trace widths, and materials are areas where quality comes into play. The via size and method of trace attachment to the via affect the signal shape and reliability. Using tear-drop trace connections to pads, vias and through hole components enhance the reliability and minimize the impedance discontinuity resulting in a cleaner signal. Using larger vias provides adequate copper for proper power distribution and more surface area to bond to where traces are interconnected. The combination provides better vibration endurance than smaller vias and traces would provide. The design has several power planes with sufficient copper weight and coverage to provide the references required for the routing plus the current and voltages needed by the various devices on the board. The larger features make the design work more difficult since there is less room to "play with" and the end result is worth it. Since 1998 when IP-BiSerial was introduced, the BiSerial family has enjoyed an excellent track record for reliability.

The PCI interface has a published set of requirements for compliance which restrict length, impedance, loading and other factors. ccPMC-BiSerial-VI is compliant with the PCI Specification. One of the features of our implentation is holding tighter tolerances than required by specification. This approach provides extra margin and allows better operation with other hardware since the error budget is essentially increased for the other portions of the sytem.

The IO section has requirements based on the IO type and the purpose for the IO. A very conservative approach has been taken to allow operation with any client requirement. The IO can be LVDS or RS-485. The IO on the connector side is differential with a 100 ohm impedance requirement. Between the FPGA and the tranceivers the IO is single ended. Each IO has separate direction, termination, and data lines to allow complete flexibilty. The design has matched length connections from the FPGA ball to the seating plane of the connector. The lengths are matched to the "mil". The Impedance is controlled and the signals routed with proper spacing to avoid cross talk etc. The other features including memory, PLL, oscillator, and power supplies are implemented within the PCB to exceed the operational requirements for those devices.

The Spartan VI has internal block RAM which can be configured in a variety of ways. Currently, up to 268 BRAMs can be configured for internal channel memory support. In addition the memory can be configured as Dual Port RAM to allow direct addressing and retransmission of repeated patterns.

Sometimes you just need more memory. DDR is available with 256 Mbytes. The DDR is supported with FPGA based FIFOs and a controller to allow more than one port to use the memory. Internal loop-back is supported. The loop-back test can be used for BIT and for software development. Programmable FIFO flags are supported on both sets of FIFOs. Programmable Almost Full, Programmable Almost Empty, plus Full, Half Full, and Empty. The programmable flags can be set to any depth to allow the software a programmable delay from event to empty or full. The interrupts can be very useful when sending or receiving messages larger than the FIFO size. The interrupts are programmable and provisions are made to allow polling. In addition DMA can be programmed to fill or empty the FIFO with sizes larger than the FIFO size. The DMA is hardware controlled to be held off when no data is available or no room is available. A new feature added with the DDR implementation is programmable boundaries to the memory. Software can set the amount allocated to each function supported by the DDR. With the "Channelized DMA"™ capability and large FIFOs the software application can have reduced interrupt counts to deal with while supporting larger and faster IO transfer rates.

ccPMC-BiSerial-VI has 32 transceivers which can be used for any combination of input and output functions. Parallel and serial data, multiple channels, and different hand-shaking schemes can be implemented with the quantity of IO with ccPMC-BiSerial-VI. Both RS-485 and LVDS are 3.3V devices allowing mixed operation if desired. RS-485 transceivers support up to 50 MHz rates. The LVDS transceivers are rated at better than 200 MHz.

The IO is available through Pn4 - See PMC-BiSerial-VI if your system required bezel IO. Each transceiver pair is isolated from the connector with zero ohm resistors. The resistors can be changed to non-zero values if your system requires. In addition the IO have resistors tied between the IO and a power plane. The plane is strappable to allow 3.3V or GND on either rail. The IO can be set to provide a high or a low condition when not driven to support half duplex operation without adding resistors to your cables. The IO are protected with transorbs for over-voltage situations.

Clock options are frequently a major factor in embedded designs. Getting the right reference to the right part of the design and allowing for local control of exact frequencies. ccPMC-BiSerial-VI has a PLL with 4 programmable outputs, reference oscillator, internal DCMs and buffering plus programable dividers instantiated within the VHDL. The PLL can be programmed to "any" fixed frequency, the DCM used to create phase variations, and local dividers to allow on-the-fly channel based frequency changes. In addition 16 signals are looped back local to the FPGA to allow derived clocks to be used as clocks with the Spartan 6 architecture.

"Channelized DMA"™ is an important feature of the ccPMC-BiSerial-VI design. With "Channelized DMA"™ you have a separate DMA engine for each transmitter and each receiver within each channel. Each state-machine can be serviced independently with DMA without requiring intervention from the host. Large data transfers can happen between multiple connections while the CPU is off doing something else. In non-channelized designs the CPU will have to intervene each time a different port needs to be serviced. With a channelized approach the hardware takes care of the local arbitration, and eliminates the intervention for better system performance and less latency.

If your situation demands a custom application we will update the Xilinx FPGA and IO components. Send us your timing and we will send you the interface. Please refer to the bottom of this page for previously completed "customerized" ccPMC-BiSerial-VI implementations.

email us your wish list or call today

ccPMC-BiSerial-VI Example Block Diagram

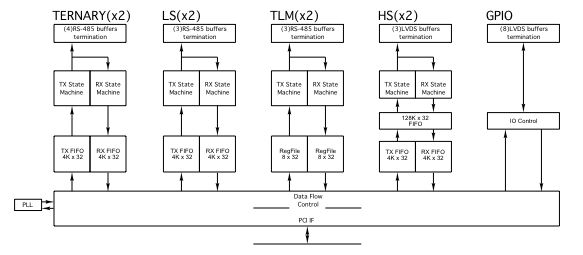

PMC-BiSerial-VI-ORB2 version block diagram

PMC Modules require a "carrier" in most cases to adapt them to the system. Dynamic Engineering has carrier solutions for a variety of formats.

PCIe implementations can be done with the PCIeBPMCX1 and PCIeBPMCX2.

PCI implementations can be done with the PCI2PMC and PCIBPMCX2.

cPCI 3U is supported with the cPCIBPMC3U32

cPCI 6U is supported with the cPCIBPMC6U.

PCI-104 is supported with the PCI104p2PMC.

The IO can be configured to support one function, one function replicated several times, or multiple functions. A real space saver when you need to have some Manchester to go with your UART and HDLC ports. A partial list of functions implemented in "Channels" includes: NRZL, Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. To support the functions the designs include: memory elements instantiated with FIFO, Dual Port RAM, register files, as well as state-machines, counters, timers, dividers, registers, CRC and Parity generation / checking, software drivers and applications, DMA [direct memory access] and the glue that goes with it. Our designs are written in VHDL and done in a heirarchy allowing direct porting of different features to create new implementations.

More than 50 customerized versions of the BiSerial family and counting. ccPMC-BiSerial-VI as well as IP-BiSerial-VI, PMC-BiSerial-VI, PC104p-BiSerial-VI, PCIe-BiSerialDb37, and PMC-BiSerial-6T20 are recommended for new designs.

The hardware is used to interface with a wide variety of equipment. What do you need to communicate with? Control? Capture data from? Please see the bottom of this page and other BiSerial implementations for descriptions and manuals for our customerized versions. We have implemented custom versions of BiSerial since 1998 when IP-BiSerial was first released.

A new custom version can be implemented in a very reasonable time. Typically a few weeks of design time for a medium sized project including the new VHDL set, Windows® or Linux driver, reference software package, and documentation. Examples of the designs performed to date are listed toward the bottom of this page and pages for other versions of BiSerial.

We can be rapid with our response because the designs are structured to allow channels to be moved in and out to create new design sets. Most designs have a fairly large component of reused "known good" VHDL that we can pull from allowing us to focus on the new functions required for your implementation. You are getting the benefit of many man-years of design and test time with each new version created. Join our high reliability clients taking advantage of our know-how to help speed your project to completion.

ccPMC-BiSerial-VI can be used along with a PCIe or other carrier/adapter to use with a variety of system types - PCI, PCIe, PC104p, VPX cPCI, etc.. Dynamic Engineering has PMC carriers for PCI, PCIexpress, cPCI, PC104p, and can do custom design´s specific to client requirements as well. Please use the pull-down menu to navigate to other Dynamic Engineering products including carriers.

PMCs are independently specified through VITA for the form factor, connectors and pinouts of the PCI signaling; you can use the ccPMC-BiSerial-VI design with any carrier from any vendor that supports standard PMCs. To support integration into a variety of systems, ccPMC-BiSerial-VI features a universal PCI voltage design to allow operation with VIO set to 3.3 or 5V.

It all starts with the PCB [Printed Circuit Board]. Quality design and quality materials are required to meet the strenuous requirements of many of our implementations. You can do the job quickly or you can do the design correctly. We pride ourselves on taking the time to put the extra work into our layouts. The quality goes in before the parts go on. In addition to routing strategy and layer counts, Via size, plating requirements, break-out trace widths, and materials are areas where quality comes into play. The via size and method of trace attachment to the via affect the signal shape and reliability. Using tear-drop trace connections to pads, vias and through hole components enhance the reliability and minimize the impedance discontinuity resulting in a cleaner signal. Using larger vias provides adequate copper for proper power distribution and more surface area to bond to where traces are interconnected. The combination provides better vibration endurance than smaller vias and traces would provide. The design has several power planes with sufficient copper weight and coverage to provide the references required for the routing plus the current and voltages needed by the various devices on the board. The larger features make the design work more difficult since there is less room to "play with" and the end result is worth it. Since 1998 when IP-BiSerial was introduced, the BiSerial family has enjoyed an excellent track record for reliability.

The PCI interface has a published set of requirements for compliance which restrict length, impedance, loading and other factors. ccPMC-BiSerial-VI is compliant with the PCI Specification. One of the features of our implentation is holding tighter tolerances than required by specification. This approach provides extra margin and allows better operation with other hardware since the error budget is essentially increased for the other portions of the sytem.

The IO section has requirements based on the IO type and the purpose for the IO. A very conservative approach has been taken to allow operation with any client requirement. The IO can be LVDS or RS-485. The IO on the connector side is differential with a 100 ohm impedance requirement. Between the FPGA and the tranceivers the IO is single ended. Each IO has separate direction, termination, and data lines to allow complete flexibilty. The design has matched length connections from the FPGA ball to the seating plane of the connector. The lengths are matched to the "mil". The Impedance is controlled and the signals routed with proper spacing to avoid cross talk etc. The other features including memory, PLL, oscillator, and power supplies are implemented within the PCB to exceed the operational requirements for those devices.

The Spartan VI has internal block RAM which can be configured in a variety of ways. Currently, up to 268 BRAMs can be configured for internal channel memory support. In addition the memory can be configured as Dual Port RAM to allow direct addressing and retransmission of repeated patterns.

Sometimes you just need more memory. DDR is available with 256 Mbytes. The DDR is supported with FPGA based FIFOs and a controller to allow more than one port to use the memory. Internal loop-back is supported. The loop-back test can be used for BIT and for software development. Programmable FIFO flags are supported on both sets of FIFOs. Programmable Almost Full, Programmable Almost Empty, plus Full, Half Full, and Empty. The programmable flags can be set to any depth to allow the software a programmable delay from event to empty or full. The interrupts can be very useful when sending or receiving messages larger than the FIFO size. The interrupts are programmable and provisions are made to allow polling. In addition DMA can be programmed to fill or empty the FIFO with sizes larger than the FIFO size. The DMA is hardware controlled to be held off when no data is available or no room is available. A new feature added with the DDR implementation is programmable boundaries to the memory. Software can set the amount allocated to each function supported by the DDR. With the "Channelized DMA"™ capability and large FIFOs the software application can have reduced interrupt counts to deal with while supporting larger and faster IO transfer rates.

ccPMC-BiSerial-VI has 32 transceivers which can be used for any combination of input and output functions. Parallel and serial data, multiple channels, and different hand-shaking schemes can be implemented with the quantity of IO with ccPMC-BiSerial-VI. Both RS-485 and LVDS are 3.3V devices allowing mixed operation if desired. RS-485 transceivers support up to 50 MHz rates. The LVDS transceivers are rated at better than 200 MHz.

The IO is available through Pn4 - See PMC-BiSerial-VI if your system required bezel IO. Each transceiver pair is isolated from the connector with zero ohm resistors. The resistors can be changed to non-zero values if your system requires. In addition the IO have resistors tied between the IO and a power plane. The plane is strappable to allow 3.3V or GND on either rail. The IO can be set to provide a high or a low condition when not driven to support half duplex operation without adding resistors to your cables. The IO are protected with transorbs for over-voltage situations.

Clock options are frequently a major factor in embedded designs. Getting the right reference to the right part of the design and allowing for local control of exact frequencies. ccPMC-BiSerial-VI has a PLL with 4 programmable outputs, reference oscillator, internal DCMs and buffering plus programable dividers instantiated within the VHDL. The PLL can be programmed to "any" fixed frequency, the DCM used to create phase variations, and local dividers to allow on-the-fly channel based frequency changes. In addition 16 signals are looped back local to the FPGA to allow derived clocks to be used as clocks with the Spartan 6 architecture.

"Channelized DMA"™ is an important feature of the ccPMC-BiSerial-VI design. With "Channelized DMA"™ you have a separate DMA engine for each transmitter and each receiver within each channel. Each state-machine can be serviced independently with DMA without requiring intervention from the host. Large data transfers can happen between multiple connections while the CPU is off doing something else. In non-channelized designs the CPU will have to intervene each time a different port needs to be serviced. With a channelized approach the hardware takes care of the local arbitration, and eliminates the intervention for better system performance and less latency.

If your situation demands a custom application we will update the Xilinx FPGA and IO components. Send us your timing and we will send you the interface. Please refer to the bottom of this page for previously completed "customerized" ccPMC-BiSerial-VI implementations.

email us your wish list or call today

PMC-BiSerial-VI-ORB2 version block diagram

PCIe implementations can be done with the PCIeBPMCX1 and PCIeBPMCX2.

PCI implementations can be done with the PCI2PMC and PCIBPMCX2.

cPCI 3U is supported with the cPCIBPMC3U32

cPCI 6U is supported with the cPCIBPMC6U.

PCI-104 is supported with the PCI104p2PMC.

ccPMC-BiSerial-VI Features

Size

Conduction Cooled PMC 74mm x 143.75mm nominal. Low profile components on rear

IO

IO is available via the PMC "user IO" connector Pn4. The differential IO is properly routed with impedance control, pitch, and space plus matched lengths across all of the pairs. Differential pairs match Dynamic Engineering PMC Carrier Differential Routing standard to allow high speed [when needed] operation. Up to 50 MHz with RS-485 and up to 200 MHz with LVDS IO types. IO protected with 400W TVS devices. IO can be terminated to a marking state for half duplex operation - build option.

Clocks

33/50 MHz PCI, 32 MHz oscillator ( other frequencies available), 4 programmable PLL inputs, Counters / Dividers / DCM for local clock control. 25, 50 and 100 MHz references from high precision source for DDR support.

Interface Types

Custom programmed interfaces are available. Please send us a timing diagram, and we can program one for you. Most interfaces can be adapted from our large library of designs within weeks including the updated VHDL, Windows or Linux Driver, reference manuals etc. We can support on-site [ours] integration to help you get your application level software working.

Alternatively choose one of the already completed versions and purchase off-the-shelf. Common requested and implemented interface types include: Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. Mix and Match. Just like but different...

Alternatively choose one of the already completed versions and purchase off-the-shelf. Common requested and implemented interface types include: Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. Mix and Match. Just like but different...

Memory

Spartan 6 - 100 is standard and has 268x1Kx16 BRAM´s to create RAM, FIFO etc., DDR 256 MBytes available.

Software Interface

Control registers are read-writeable

Windows®, Linux reference SW and Drivers

Windows®, Linux reference SW and Drivers

Interrupts

Software programmable interrupts on status, errors, completion of transfer, DMA, FIFO levels, custom events. Status can be polled for non-interrupt driven operation as well.

Power Requirement

+5V, 3.3V from PMC input, 5V converted to 2.5, 1.2, 1.5, .75 with local DC:DC power supplies for efficient power conversion.

LEDs

1.2V good, 1.5V good, Lock achieved [100 MHz has achieved lock within FPGA].

Volatility

Reliability

TBD million hours. Bellcore. GB 25c

PMC-BiSerial-VI Benefits

Speed

ccPMC-BiSerial-VI can offload your CPU and increase system speed. With the large amount of memory and high speed IO data can be captured and stored in parallel with DMA transfers to the host memory. Similarly DMA can be used to load the memory to transmit out the IO. Large and small data packets can be stored to keep the IO running with a high duty cycle and efficient transfer. With the large memory, large DMA transfers can be set-up offloading the host from the interrupts associated with smaller transfers.

Price

System level cost is best when reasonably priced reliable hardware is used and NRE minimized. With ccPMC-BiSerial-VI, driver support, reference software, history of reliable operation, and fantastic client support your cost per unit and overall costs are attractive.

Ease of Use

ccPMC-BiSerial-VI is designed to be easy to use. Direct access to all features, aligned registers for larger access types, programmable features to allow personalization for your system. Please download the manuals and see for yourself. Reference software is provided in source form to get you started.

Availability

There are two basic models with LVDS or RS-485 IO types. Both are stocked allowing a quick "PCO" to reflash and retest into your configuration. Already completed designs can be ordered with a minimal delay in delivery. New NRE required designs will have some delay to implement, integrate and test.

PMC Specification Compatibility

ccPMC-BiSerial-VI is compliant per the VITA PMC/CMC specifications for conduction cooled hardware Tested with PCI and PCie based carriers. All Dynamic Engineering PMC Modules are compatible with the PCIeBPMCX1, ccPMC-BiSerial-VI will operate with any PMC specification compliant carrier board.

Part Number: ccPMC-BiSerial-VI

Ordering Options

- ccPMC-BiSerial-VI Standard board - with RS485 IO , Industrial temperature components.

- -LVDS Switch to LVDS IO

- -ROHS Use ROHS processing. Standard processing is ""leaded"

- -CC Option to add Conformal Coating

- -XXX See Models section for customized versions and replace XXX with type "GPIO" for example

PMC-BiSerial-VI Drivers

Software Support for ccPMC-BiSerial-VI-XXX includes: Windows® , and Linux compliant drivers

Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of ccPMC-BiSerial-VI implemented. When custom versions are ordered the NRE will include providing Windows, or Linux [VxWorks by special arrangement] packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of ccPMC-BiSerial-VI implemented. When custom versions are ordered the NRE will include providing Windows, or Linux [VxWorks by special arrangement] packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

ccPMC-BiSerial-VI Models

ccPMC-BiSerial-VI-UART

This design scheduled to be ported - available soon

8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. [higher with PLL reference selected] Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.

UnPacked mode 8 bit data is assumed mimicking standard UART operation

Packed mode 32 bit data is assumed allowing 4 characters to be read/written at a time.

Packetized mode allows for non-LW data lengths, and retains most of the efficiency of LW packing. Odd lengths [non LW boundaries] are loaded with the complete LW´s first then the remainder. The Packet length FIFO is programmed with the length to send. The Packet lengths can be loaded to transmit with minimal HW delay between Packets or with a programmed delay.

Alternate Packetized mode: 3 data bytes per LW with the packet descriptor information built into the 4th byte.

Test mode SW controls the output pattern to allow for programmed errors on certain characters sent.

Programmable timers are available to control the time between packets sent and as a master timer to start new bursts of packets. In addition the Alternate Packet mode supports automatic tristate control and automatic transmit enable/disable to support the packet burst timing. Please see the HW manual for more information.

Download the PMC BiSerial VI UART Hardware manual.

Download the PMC BiSerial VI UART Windows Driver manual.

Download the PMC BiSerial VI UART Linux Driver manual.

ccPMC-BiSerial-VI-GPIO

GPIO 32 Differential IO in a General Purpose IO configuration

Change of State [COS] with independent Rising and Falling selections to allow for data capture on either, neither, or both edges. Edge or Level selection to allow treating IO as level based. Separate interrupt enables for each IO. Independent polarity selection. Multiple programmable COS rates based on programmable PLL and local oscillator [16 bit divisor]. Dip Switch for user purposes. Temperature sensor. All bits can be read-back. Programmable Tx bits. Design supports internal loop-back. Unified driver supports ccPMC and PMC models.

DMA support with 8Kx32 FIFO for user purposes.

Driver has utilities for programming the PLL using the "JED" file, reading the temperature, and managing all of the features.

Reference manuals from the TTL version. Differential Manual in edit

Download the ccPMC-BiSerial-VI-GPIO Win10 Driver Package Manual

Download the Parallel-TTL-GPIO Linux Driver Package Manual

Download the ccPMC-BiSerial-VI-GPIO HW Manual

ccPMC-BiSerial-VI-ORN1

SDLC and NRZL

32 bit parallel port with control register to map in Port functions.

2 ports of SDLC supported with Dual Ported RAM, programmable Tx rate, internal or external clock reference, programmable interrupts.

2 ports of NRZ/NRZL with programmable Tx rate, programmable active edge for the clock, programmable sense for the data, programmable MSB or LSB first order of bit, programmable length of message with a separate Packet FIFO to allow message by message length changes. Additional features include a Packet Gap timer, programmable end of packet timer, programmable Almost Full and Almost Empty status bits, status for OverFlow and Under Run, User Interrupt, FIFO loop-back mode.

Dip Switch for user purposes. Temperature sensor. All bits can be read-back.

Driver has utilities for programming the PLL using the "JED" file, reading the temperature, and managing all of the features.

Download the ccPMC-BiSerial-VI-ORN1 Win10 Driver Package Manual

Download the ccPMC-BiSerial-VI-ORN1 HW Manual

Download the ccPMC-BiSerial-VI-ORN1 VxWorks Driver Package Manual

Download the ccPMC-BiSerial-VI-ORN1 Linux Driver Package Manual

This design scheduled to be ported - available soon

8 UART I/O ports each consisting of RS-485 transmit and receive data. [LVDS is an ordering option] The UART interface uses a 16x clock to detect received data bits. Received data is filtered with the port reference clock to remove line glitches. The interface can operate at up to 2 Mbits/second using a 32 MHz clock. [higher with PLL reference selected] Reference clock for each port is selectable between the 32 MHz reference and a user programmed PLL frequency. Each UART port has 255 x 32 FIFO for transmit and another 255x32 for receive in addition to Packet Definition FIFOs. DMA support on all channels. 5 modes can be selected per fully independent node: Standard UART (unpacked), Packed, Packetized, Alternate Packetized, and Test. Options for Bezel and Rear IO.

Programmable timers are available to control the time between packets sent and as a master timer to start new bursts of packets. In addition the Alternate Packet mode supports automatic tristate control and automatic transmit enable/disable to support the packet burst timing. Please see the HW manual for more information.

Download the PMC BiSerial VI UART Hardware manual.

Download the PMC BiSerial VI UART Windows Driver manual.

Download the PMC BiSerial VI UART Linux Driver manual.

ccPMC-BiSerial-VI-GPIO

GPIO 32 Differential IO in a General Purpose IO configuration

Change of State [COS] with independent Rising and Falling selections to allow for data capture on either, neither, or both edges. Edge or Level selection to allow treating IO as level based. Separate interrupt enables for each IO. Independent polarity selection. Multiple programmable COS rates based on programmable PLL and local oscillator [16 bit divisor]. Dip Switch for user purposes. Temperature sensor. All bits can be read-back. Programmable Tx bits. Design supports internal loop-back. Unified driver supports ccPMC and PMC models.

DMA support with 8Kx32 FIFO for user purposes.

Driver has utilities for programming the PLL using the "JED" file, reading the temperature, and managing all of the features.

Reference manuals from the TTL version. Differential Manual in edit

Download the ccPMC-BiSerial-VI-GPIO Win10 Driver Package Manual

Download the Parallel-TTL-GPIO Linux Driver Package Manual

Download the ccPMC-BiSerial-VI-GPIO HW Manual

ccPMC-BiSerial-VI-ORN1

SDLC and NRZL

Driver has utilities for programming the PLL using the "JED" file, reading the temperature, and managing all of the features.

Download the ccPMC-BiSerial-VI-ORN1 Win10 Driver Package Manual

Download the ccPMC-BiSerial-VI-ORN1 HW Manual

Download the ccPMC-BiSerial-VI-ORN1 VxWorks Driver Package Manual

Download the ccPMC-BiSerial-VI-ORN1 Linux Driver Package Manual