IP-BiSerial-VI

IP Module with Spartan 6 FPGA, PLL, 24 Independent Differential IO - RS422, RS-485, LVDS

Order This Item

IP-BiSerial-VI Description

- Driver included with purchase

- Standard Type II module

- 8↔32 MHz. operation

- 24 independent differential IO. Each with programmable termination and direction.

- RS-485, RS-422, LVDS and mixed

- Spartan 6 FPGA with BRAM for FIFO or RAM implementation

- PLL with 4 clock references

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature standard.

- ROHS and Standard processing available

IndustryPack® Modules are an important part of solutions for Embedded situations. Rugged, small, light .. just right for many applications. With IP-BiSerial-VI many communications, telemetry, command and control applications can be handled.

The first revision of IP-BiSerial circa 1998 has more than 16 customized versions. IP-BiSerial-VI utilizes current technology to expand the IO count from 9 to 24, increase the FPGA capability, add PLL´s, offer LVDS and RS-485 based solutions. A lot of capability in a small package.

The first two client designs ultilizing IP-BiSerial-VI include an 8 channel Counter Timer function with internal and external clocking and plus a One Shot mode with Software and External triggering. The second module is a two channel dual function serial interface. Both versions have Windows, and Linux support. The counter timer module also has VxWorks support.

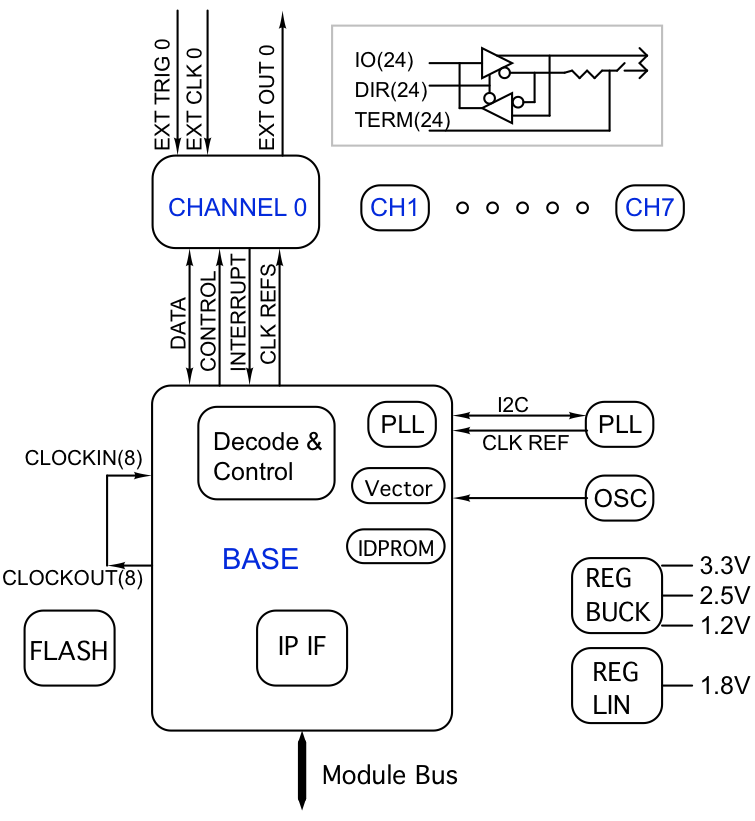

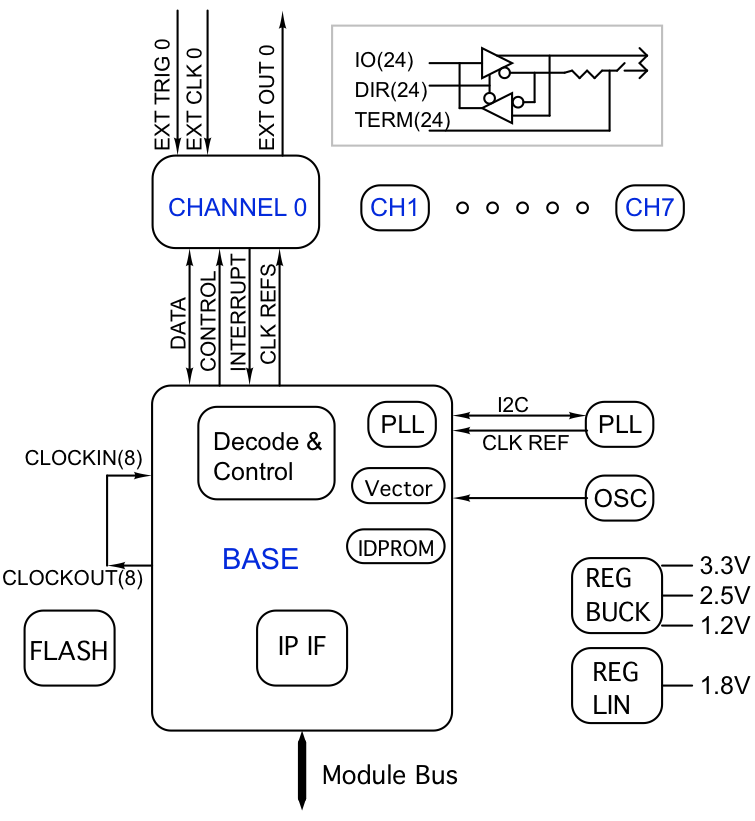

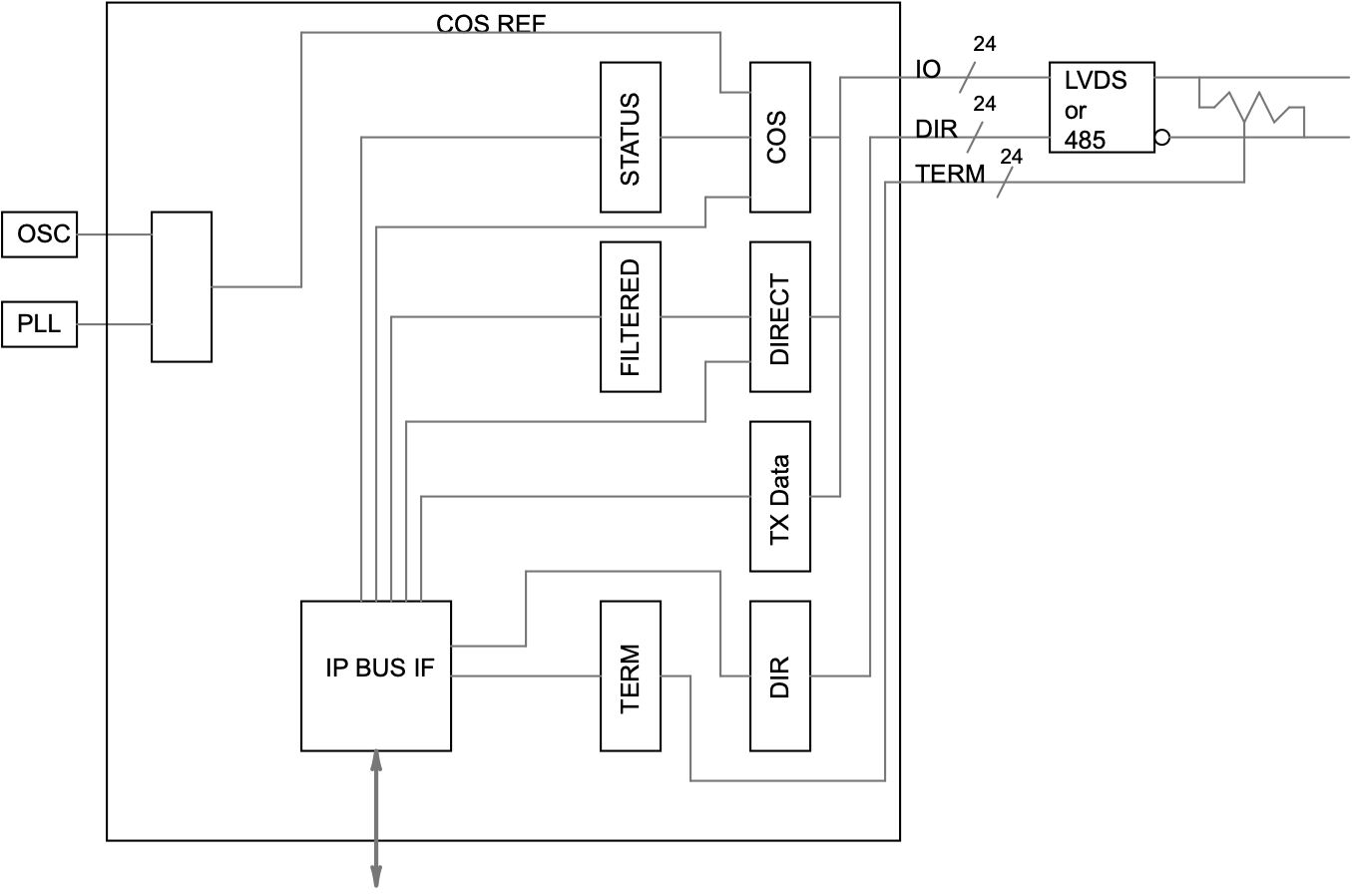

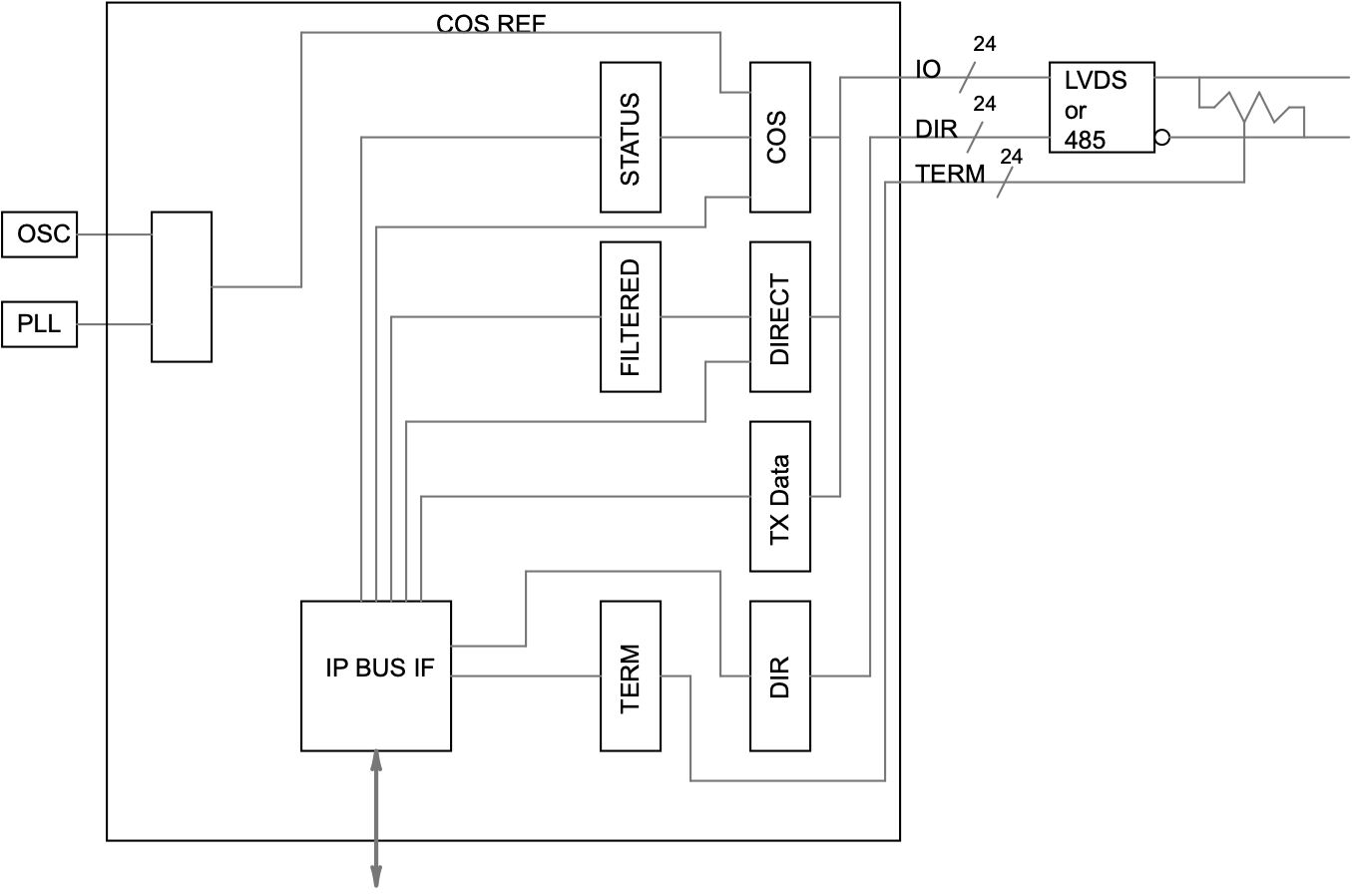

The CTRB model Block Diagram shown above is a good example of the features IP-BiSerial-VI has to offer. CTRB has eight channels/ports each using 3 Differential IO. In this case the IO standard is RS-485. The devices can be substitued with LVDS compatible parts if desired. Each of the ports has an external clock input, external trigger input and an output. Each port is independent, plus has a SW option to use a master start control to allow synchronization across selected ports. Each channel has a 32 bit counter which can operate from the external clock or the internal reference. When in Counter/Timer mode the Output is pulsed when the programmed count expires. The counter can automatically reload to create a pulse stream or be set as a one-time event. An interrupt can be generated when the time expires allowing use for system timing. In addition the port can be programmed to operate in One Shot mode where a software trigger or external event causes a programmed length pulse to be generated.

Each of the IO have Direction, and Termination controls as shown. The CTRB function has defined IO allowing the Direction and Termination controls to be set in HW for this design.

The controls can be under HW or SW control depending on the requirements of the design. For example, 1/2 duplex operation may require SW intervention or be controlled via HW when the timing is known. With the independent controls serial, parallel, full and half duplex, special sequence control etc. are programmable within the FPGA.

Many designs have been implemented and integrated into client systems using IP, PMC, PCIe based BiSerial designs. We can port from the other versions to IP-BiSerial-VI with the caveat of number of IO. In many cases we have a good portion of what your requirement needs and can adapt to your specific needs more efficiently than starting from scratch with a new design. Further the IP version can be implemented in a number of system types with our off-the-shelf carriers.

IndustryPack® Modules require a "carrier" in most cases to adapt them to the system. Dynamic Engineering has carrier solutions for a variety of formats.

PCIe implementations can be done with the PCIe3IP and PCIe5IP.

PCI implementations can be done with the PCI3IP and PCI5IP.

cPCI 3U is supported with the cPCI2IP. Up to 2 IP-BiSerial-VI per slot

cPCI 6U is supported with the cPCI4IP. Up to 4 IP-BiSerial-VI per slot

PC104p is supported with the PC104pIP.

PC104p situations with a custom mechanical can be done with the PC104p4IP. Up to 4 IP-BiSerial-VI per slot

VPX 3U is supported with the VPX2IP. Up to 2 IP-BiSerial-VI per slot

The first revision of IP-BiSerial circa 1998 has more than 16 customized versions. IP-BiSerial-VI utilizes current technology to expand the IO count from 9 to 24, increase the FPGA capability, add PLL´s, offer LVDS and RS-485 based solutions. A lot of capability in a small package.

The first two client designs ultilizing IP-BiSerial-VI include an 8 channel Counter Timer function with internal and external clocking and plus a One Shot mode with Software and External triggering. The second module is a two channel dual function serial interface. Both versions have Windows, and Linux support. The counter timer module also has VxWorks support.

The CTRB model Block Diagram shown above is a good example of the features IP-BiSerial-VI has to offer. CTRB has eight channels/ports each using 3 Differential IO. In this case the IO standard is RS-485. The devices can be substitued with LVDS compatible parts if desired. Each of the ports has an external clock input, external trigger input and an output. Each port is independent, plus has a SW option to use a master start control to allow synchronization across selected ports. Each channel has a 32 bit counter which can operate from the external clock or the internal reference. When in Counter/Timer mode the Output is pulsed when the programmed count expires. The counter can automatically reload to create a pulse stream or be set as a one-time event. An interrupt can be generated when the time expires allowing use for system timing. In addition the port can be programmed to operate in One Shot mode where a software trigger or external event causes a programmed length pulse to be generated.

Each of the IO have Direction, and Termination controls as shown. The CTRB function has defined IO allowing the Direction and Termination controls to be set in HW for this design.

The controls can be under HW or SW control depending on the requirements of the design. For example, 1/2 duplex operation may require SW intervention or be controlled via HW when the timing is known. With the independent controls serial, parallel, full and half duplex, special sequence control etc. are programmable within the FPGA.

Many designs have been implemented and integrated into client systems using IP, PMC, PCIe based BiSerial designs. We can port from the other versions to IP-BiSerial-VI with the caveat of number of IO. In many cases we have a good portion of what your requirement needs and can adapt to your specific needs more efficiently than starting from scratch with a new design. Further the IP version can be implemented in a number of system types with our off-the-shelf carriers.

IndustryPack® Modules require a "carrier" in most cases to adapt them to the system. Dynamic Engineering has carrier solutions for a variety of formats.

PCIe implementations can be done with the PCIe3IP and PCIe5IP.

PCI implementations can be done with the PCI3IP and PCI5IP.

cPCI 3U is supported with the cPCI2IP. Up to 2 IP-BiSerial-VI per slot

cPCI 6U is supported with the cPCI4IP. Up to 4 IP-BiSerial-VI per slot

PC104p is supported with the PC104pIP.

PC104p situations with a custom mechanical can be done with the PC104p4IP. Up to 4 IP-BiSerial-VI per slot

VPX 3U is supported with the VPX2IP. Up to 2 IP-BiSerial-VI per slot

IP-BiSerial-VI Features

Size

1.8x3.9 inches nominal Type II with low profile components on rear

IO

24 differential IO each with independent Direction and Termination control. LVDS, RS-485, RS-422 supported. Differentially routed with controlled impedance matched length traces. Differential pairs match Dynamic Engineering IP Carrier Differential Routing standard to allow high speed [when needed] operation. Up to 50 MHz with RS-485 and up to 200 MHz with LVDS IO types.

Clocks

Compatible with 8 and 32 MHz IP bus operation. 50 MHz oscillator, 4 programmable PLL inputs

IP Decoding

Set-up for byte, word, or multiple word payload [x32, x64 etc See PCIe carriers]. LW registers are LW aligned to allow use of 32 bit accesses. FIFO´s can accept/source back-to-back transfers. ID, IO, INT, MEM spaces supported.

Memory

Spartan 6 - 25 is standard and has 52x1Kx16 BRAM´s to create RAM, FIFO etc.

Software Interface

Control registers are read-writeable

Windows®, Linux, VxWorks reference SW and Drivers

Windows®, Linux, VxWorks reference SW and Drivers

Interrupts

Programmable interrupts, Almost Full, Almost Empty, End of Transmission/Reception, Pulse generated etc.

Power Requirement

+5V converted to 3.3V, 2.5, 1.2 with local DC:DC power supplies for efficient power conversion. 1.8V for FLASh with linear regulator.

LED´s

On rear indicating Main DC/DC [3.3V] is in regulation.

Volatility

Statement of Volatility

Reliability

TBD million hours. Bellcore. GB 25c

IP-BiSerial-VI Benefits

Speed

IP-BiSerial-VI can offload your CPU and increase system speed. The IO rate is high compared to typical IP Module uses allowing for system upgrades, replacement of older boards, and relocating processes done in SW to the HW as needed.

Price

System level cost is best when reasonably priced reliable hardware is used and NRE minimized. With IP-BiSerial-VI, driver support for the carrier and IP level, reference software, history of reliable operation, and fantastic client support your cost per unit and overall costs are attractive.

Ease of Use

IP-BiSerial-VI is designed to be easy to use. Direct access to all features, aligned registers for larger access types, programmable features to allow personalization for your system. Please download the manuals and see for yourself. Reference software is provided in source form to get you started.

Availability

There are two basic models with LVDS or RS-485 IO types. Both are stocked allowing a quick "PCO" to reflash and retest into your configuration. Already completed designs can be ordered with a minimal delay in delivery. New NRE required designs will have some delay to implement, integrate and test.

IP Specification Compatibility

IP-BiSerial-VI is compliant per the VITA 4 - 1995 specification. Tested with PCI and PCIe based carriers. All Dynamic Engineering IP Modules are compatible with the PCIe3IP, PCIe5IP, VPXI2IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP etc. IP-BiSerial-VI will operate with any IP specification compliant carrier board.

Part Number: IP-BiSerial-VI

Ordering Options

- IP-BiSerial-VI Standard board - with RS485 IO , Industrial temperature components.

- -LVDS Switch to LVDS IO

- -ROHS Use ROHS processing. Standard processing is ""leaded"

- -CC Option to add Conformal Coating

- -XXX See Models section for predefined versions and replace XXX with type

- Types

- -CTRB 8 ports: Counter and One Shot with programmable options.

- -GPIO Programmable 24 bit parallel port with interrupts, change of state detection, independent per bit Tx/Rx, Termination, Polarity, Rising, Falling, Edge/Level, Interrupt Enable plus PLL and Ocillator reference selection.

- -SIB 2 ports: In SDC/SDT Mode the Clock and Gate are received, the data is transmitted by the SDT and received by the SDC. In USIP/USOP Mode Data, Clock, and Gate are transmitted by the USOP side of the port and received by USIP.

- -BA27 Programmable 16 or 32 bit data transfer [Clock and Data]. RS485 or LVDS IO. Programmable Parity, bit direction [Msb/Lsb first]. Programmable Interrupts.,Almost Empty, and Almost Full thresholds.

- -USER model for User programmable IO. Comes with XC6SLX25-2FTG256I installed standard RS485 IO.

- -USER-LVDS model for User programmable IO. Comes with XC6SLX25-2FTG256I installed standard LVDS IO.

- -USER-M# model for User programmable IO. Comes with XC6SLX25-2FTG256I installed standard Mixed IO. Replace # with number of LVDS IO. for -M types 1-23 [24 = -LVDS model]. "-M14" would select 14 LVDS and the remainder [10] RS485. Populated starting with IO(0) and progressing toward IO(23) for the specified quantity.

IP-BiSerial-VI Drivers

Software Support for IP-BiSerial-VI-XXX includes: Windows® 10, VxWorks, and Linux compliant drivers

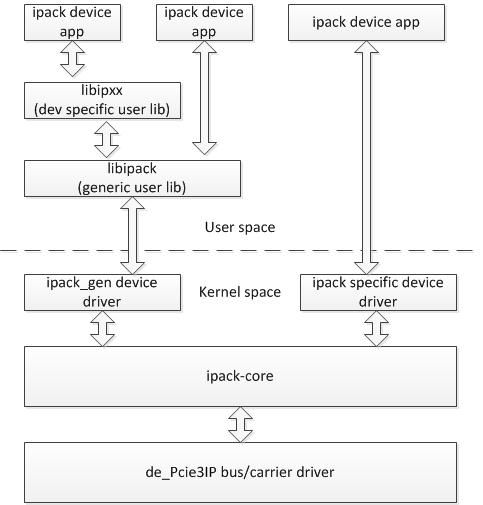

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of IP-BiSerial-VI implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

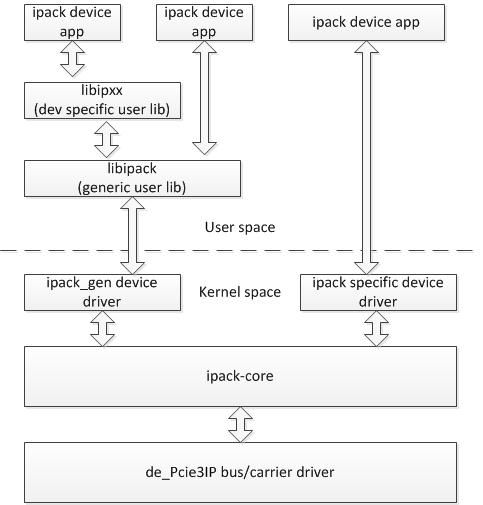

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of IP-BiSerial-VI implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

IP-BiSerial-VI predefined models

Click on the links to Download selected manuals in PDF format.

Download the IP Carrier and Module Quick Start guide for Windows®10

IP Carrier and Module Quick Start guide for Windows®10

USER Download the User Manual for Reference design supplied with self designed versions. Sometimes you need or just want to do the design yourself. Recommended to use with the User Programmable package, we supply a complete VHDL package and instruction manual. Offered with -485, -LVDS, and Mixed IO types.

GPIO Parallel Port with COS (Change of State)

Block Diagram for GPIO implementation

Differential IO with independent operation per bit. Tx Data, Termination, Direction, Polarity, Edge / Level, Rising Edge, Falling Edge registers. LW aligned to allow use of LW accesses if your carrier supports this feature. Direct read of IO or Filtered data with EdgeLevel and Polariy applied. 3 interrupt selections per bit. Designed to allow polled operation. PLL and Oscilator references with divider to support COS. Win10 and Linux reference SW packages

GPIO Model Hardware Manual

GPIO Model Win10 Manual

GPIO Model Linux Manual

CTRB Each of the 8 channels has the same capabilities. Counter and One Shot support with several programmable options.

In the Counter Modes the options are for internal and external clock input, length of time until the timer expires, continuous or single count down, interrupt or polled operation.

In the One Shot Modes the options include internal or external clock reference, internal or external trigger, rising or falling edge [with external trigger], length of output pulse, interrupt or polled operation.

CTRB Model Hardware Manual

CTRB Model Win7 Manual

VxWorks IP Module Manual

IP Carrier Linux Manual

Linux IP Module Manual

SIB Each of the 2 channels has the same capabilities. SDC/SDT or USIP/USOP support with several programmable options .

In SDC/SDT Mode the Clock and Gate are received, the data is transmitted by the SDT and received by the SDC portion of the interface. CTS is provided but not required for operation. Interrupt or polled operation.

In USIP/USOP Mode the Data, Clock, and Gate are transmitted by the USOP side of the channel and received by USIP. In addition USIP transmits CTS to indicate USOP can transmit data. The Clear To Send signal is deasserted when the Rx FIFO is almost full. The Transmitter detects the deassertion and stops at the next word boundary. This may happen 2 words after deassertion if the deassertion is near the end of a word. CTS can be inverted and disabled via the channel control register. CTS is normally asserted ´1´ when data can be transmitted, and ´0´ to hold off. With the CTSsense bit ´0´ can mean transmit and ´1´ hold off to match your system. When disabled the line is held in the hold off state based on the CTS sense definition.

SIB Model Hardware Manual

SIB Model Win7 Manual

IP Carrier Linux Manual

Linux IP Module Manual

VxWorks IP Module Manual

BA27 Full Duplex operation

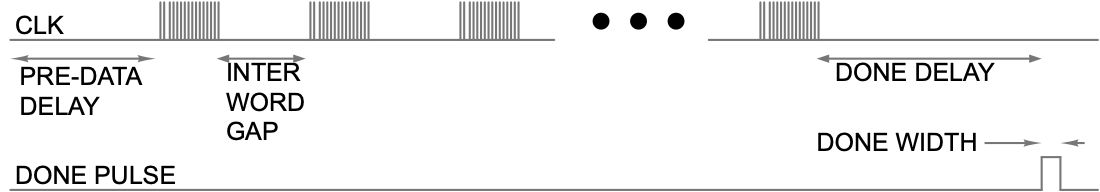

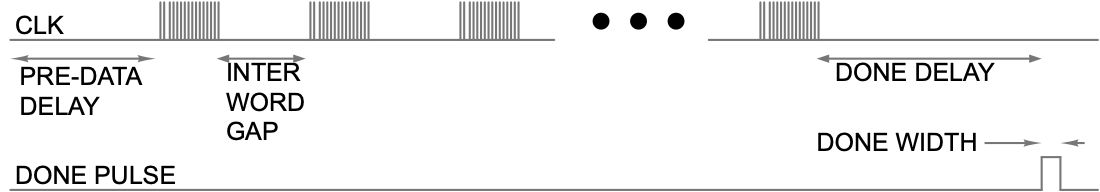

Overall timing for MultiCycle mode operation.

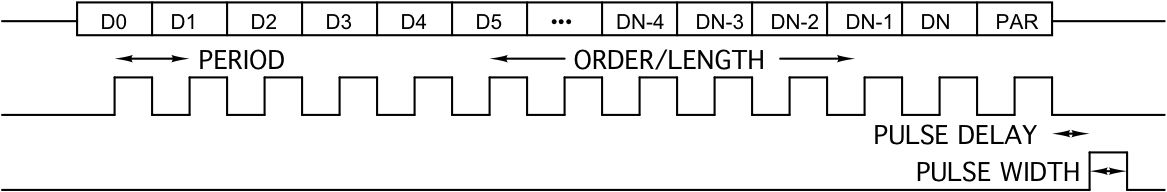

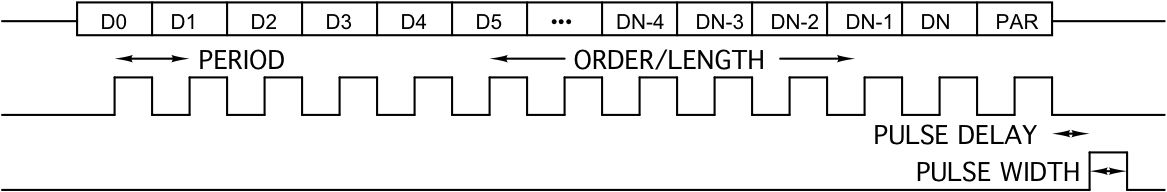

Per word transmitted timing in SingleCycle mode

Ported from Q1 and BA13 designs on IP-BiSerial platform and enhanced: 4Kx16 Tx and Rx FIFO. Programmable 16 or 32 bit data transfer [Clock and Data]. Programmable Done Pulse - delay to pulse and width of pulse. Pre-Data Delay - programmable delay from SW start or external trigger. Inter-word gap - programmable delay between words sent in MultiCycle mode. Programmable external trigger use including polarity. Programmable width of transmitted trigger. RS485 or LVDS IO. Programmable Parity, bit direction [Msb/Lsb first]. Programmable Interrupts. Programmable Almost Empty, and Almost Full thresholds. 1MHz. or divided clock [based on 50 Mhz] transmit rate. Auto-baud Rx input. 16 bit parallel port.

BA27 Model Hardware Manual

BA27 Model Win10 Manual

BA27 Model Win7 Manual

Download the IP Carrier and Module Quick Start guide for Windows®10

IP Carrier and Module Quick Start guide for Windows®10

USER Download the User Manual for Reference design supplied with self designed versions. Sometimes you need or just want to do the design yourself. Recommended to use with the User Programmable package, we supply a complete VHDL package and instruction manual. Offered with -485, -LVDS, and Mixed IO types.

GPIO Parallel Port with COS (Change of State)

Block Diagram for GPIO implementation

Differential IO with independent operation per bit. Tx Data, Termination, Direction, Polarity, Edge / Level, Rising Edge, Falling Edge registers. LW aligned to allow use of LW accesses if your carrier supports this feature. Direct read of IO or Filtered data with EdgeLevel and Polariy applied. 3 interrupt selections per bit. Designed to allow polled operation. PLL and Oscilator references with divider to support COS. Win10 and Linux reference SW packages

GPIO Model Hardware Manual

GPIO Model Win10 Manual

GPIO Model Linux Manual

CTRB Each of the 8 channels has the same capabilities. Counter and One Shot support with several programmable options.

In the Counter Modes the options are for internal and external clock input, length of time until the timer expires, continuous or single count down, interrupt or polled operation.

In the One Shot Modes the options include internal or external clock reference, internal or external trigger, rising or falling edge [with external trigger], length of output pulse, interrupt or polled operation.

CTRB Model Hardware Manual

CTRB Model Win7 Manual

VxWorks IP Module Manual

IP Carrier Linux Manual

Linux IP Module Manual

SIB Each of the 2 channels has the same capabilities. SDC/SDT or USIP/USOP support with several programmable options .

In SDC/SDT Mode the Clock and Gate are received, the data is transmitted by the SDT and received by the SDC portion of the interface. CTS is provided but not required for operation. Interrupt or polled operation.

In USIP/USOP Mode the Data, Clock, and Gate are transmitted by the USOP side of the channel and received by USIP. In addition USIP transmits CTS to indicate USOP can transmit data. The Clear To Send signal is deasserted when the Rx FIFO is almost full. The Transmitter detects the deassertion and stops at the next word boundary. This may happen 2 words after deassertion if the deassertion is near the end of a word. CTS can be inverted and disabled via the channel control register. CTS is normally asserted ´1´ when data can be transmitted, and ´0´ to hold off. With the CTSsense bit ´0´ can mean transmit and ´1´ hold off to match your system. When disabled the line is held in the hold off state based on the CTS sense definition.

SIB Model Hardware Manual

SIB Model Win7 Manual

IP Carrier Linux Manual

Linux IP Module Manual

VxWorks IP Module Manual

BA27 Full Duplex operation

Overall timing for MultiCycle mode operation.

Per word transmitted timing in SingleCycle mode

Ported from Q1 and BA13 designs on IP-BiSerial platform and enhanced: 4Kx16 Tx and Rx FIFO. Programmable 16 or 32 bit data transfer [Clock and Data]. Programmable Done Pulse - delay to pulse and width of pulse. Pre-Data Delay - programmable delay from SW start or external trigger. Inter-word gap - programmable delay between words sent in MultiCycle mode. Programmable external trigger use including polarity. Programmable width of transmitted trigger. RS485 or LVDS IO. Programmable Parity, bit direction [Msb/Lsb first]. Programmable Interrupts. Programmable Almost Empty, and Almost Full thresholds. 1MHz. or divided clock [based on 50 Mhz] transmit rate. Auto-baud Rx input. 16 bit parallel port.

BA27 Model Hardware Manual

BA27 Model Win10 Manual

BA27 Model Win7 Manual