cPCI2PMC

cPCI 3U adapter for PMC

Order This Item

cPCI2PMC Description

- Industrial Temperature

- PMC position with PCI interface supporting PCI and PCI-X [32/33 ↔ 64/133]

- Plug and Play operation

- Local Power filtering

- 3U 4HP cPCI

- "Zero Slot Fan"™ Compatible

- Bezel I/O and Jn4 I/O for PMC

- 1 Year Warranty Standard. Extended Warranty Available.

- ROHS and Standard Processing Available

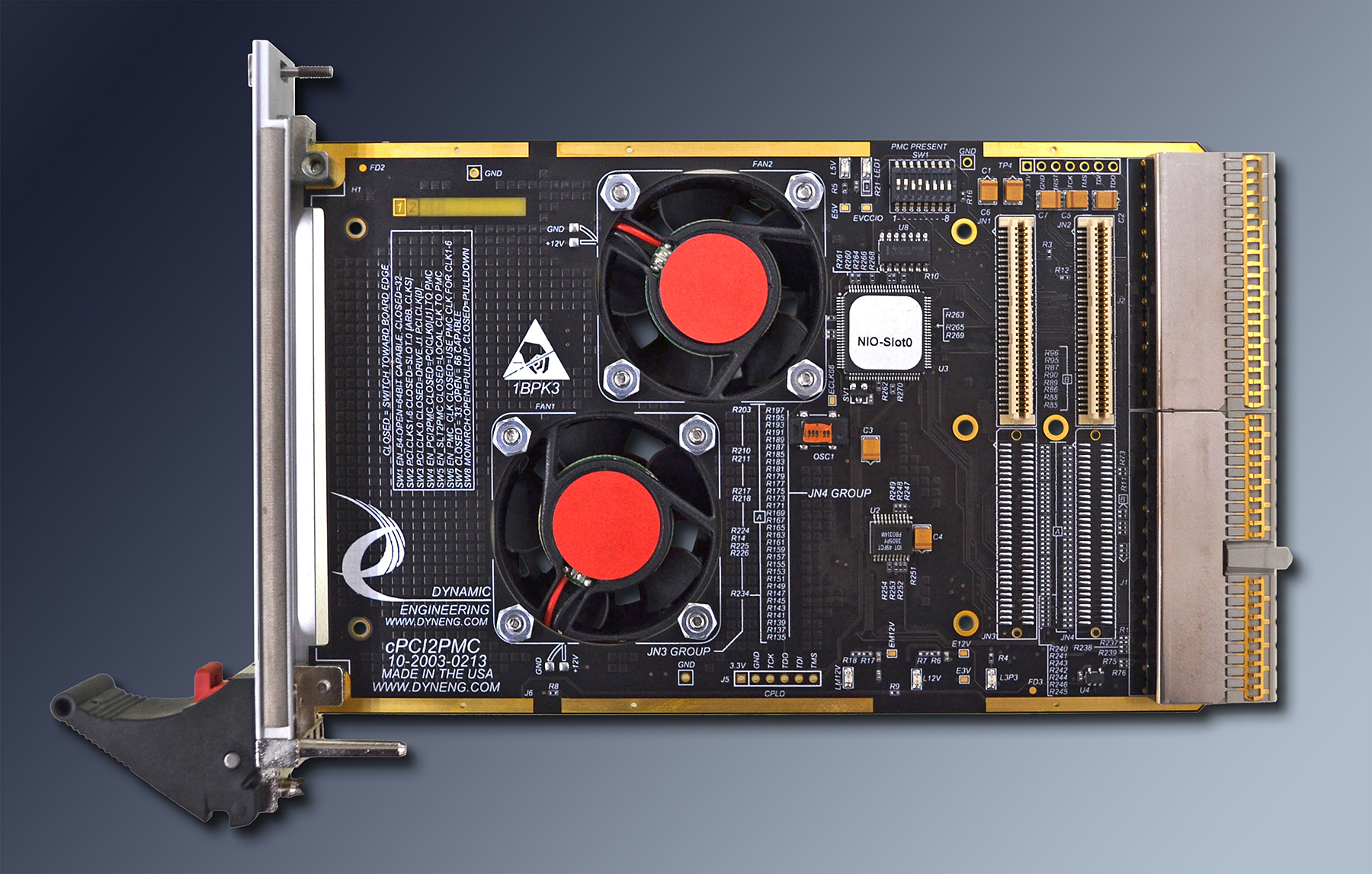

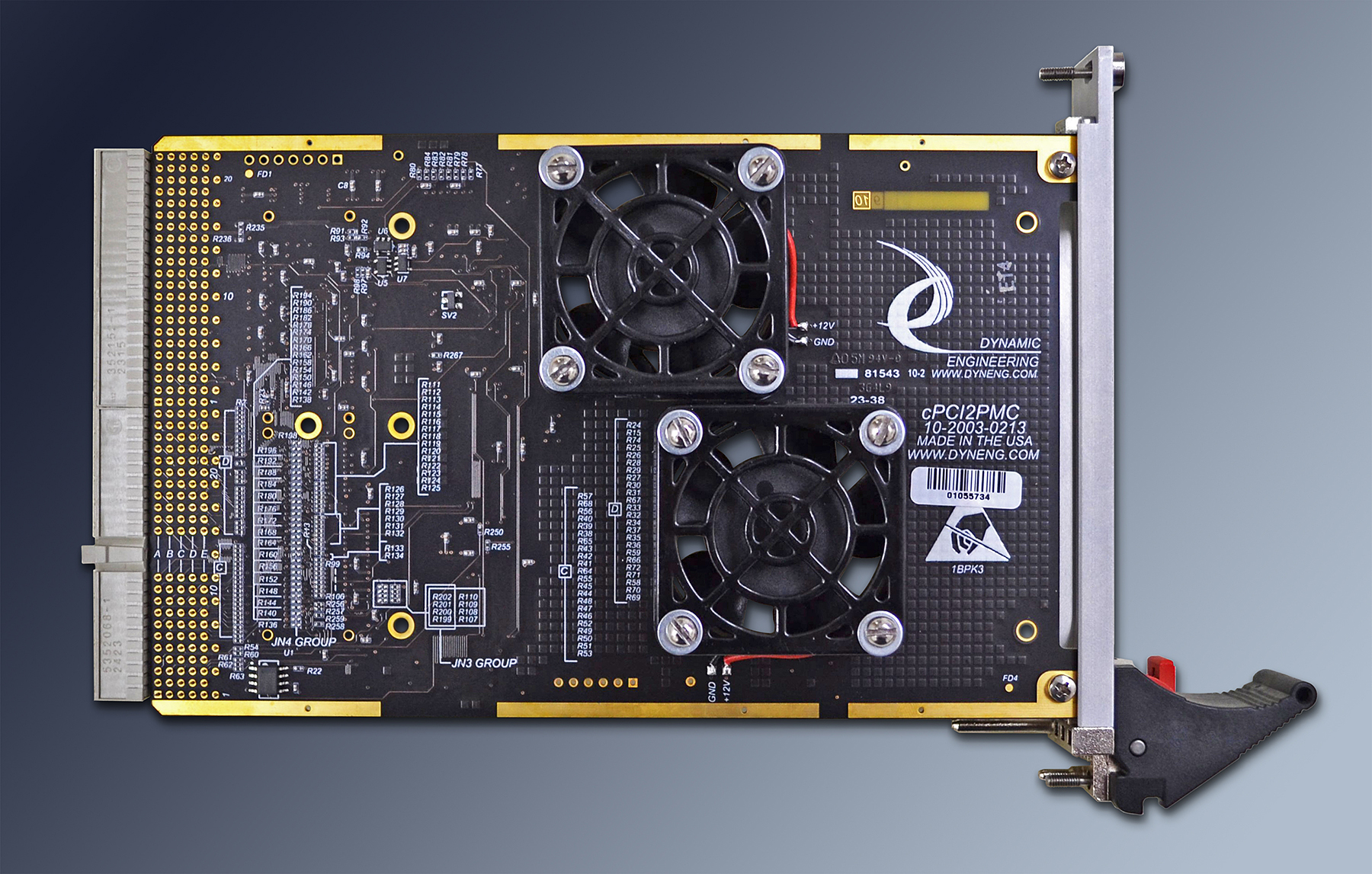

cPCI2PMC (cPCI to PMC) adapter/carrier converter card provides the ability to install one PMC or PrPMC card into a standard cPCI slot. cPCI2PMC has a PMC card slot mounted to a universal 3U 4HP cPCI card. Suitable for 32/64 with 33/ 66 MHz bus operation. The PMC user IO connector Pn4 is optionally connected to J2 for rear panel IO. The PMC bezel connector is mounted though the cPCI mounting bracket. Optional Slot 0 operation with Bus Arbitration, Reset, clock distribution provided.

The cPCI bus is buffered with 10 ohm series resistors. The PCI clock is distributed with a zero delay buffer. The cPCI2PMC design is passive with no added delays to access the PMC hardware. The traces are carefully routed with proper attention paid to the impedance and reference planes to maximize compatibility with your cPCI system. The passive design of the cPCI2PMC reduces system latency.

The PCI bus is interconnected to the PMC via 64 bit 66 MHz capable layout. The slower and more narrow device will determine the interface characteristics. The M66EN selection allows the user to specify the PCI speed capabilities. M66EN is interconnected between the cPCI bus, jumper, and PMC device.

cPCI VIO is interconnected to the PMC directly. The PCI backplane will determine the bus voltage reference. The voltage select pins are not installed on the cPCI2PMC. It is for the user to properly select the PMC and cPCI motherboard for cPCI voltage level considerations. Many PMC´s are "universal" and can work with 3.3 or 5V cPCI backplanes. If you need to use a 3.3V card on a 5V backplane or vice-versa please consider the cPCIBPMC3U64ET design. The bridged implementation provides level shifting between the cPCI and PMC buses.

cPCI2PMC follows the PMC specs for maximum power consumption and heat dissipation. The power is routed from the cPCI to PMC connectors with mini-planes. Each of which is rated for more than the maximum PMC draw. 3.3V, 5V, VIO, +12V, -12V.

The individual pins on the JN4 (PN4) connector are accessible when the IO option is specified. With 3U cPCI , J2 has two definitions - in a 64 bit PCI implementation J2 has the upper A/D and control signals, and in a 32 bit PCI implemention J2 has the rear panel IO. With resistor jumpers the IO or the PCI signals can be connected to J2. Please be sure to specify -IO, -64, or blank [neither]. The routing is impedance controlled and matched length.

With the RevK and later boards cooling fans are an available option. High velocity 12V fans can be mounted to the rear or medium velocity "Zero Slot" fans can be mounted to the board. WIth the "Zero Slot" fans no extra cPCI positions are used for the fan, and the fans are legal for a PMC height and cPCI height specifications. Approximately 5 CFM per installed "Zero Slot" fan. The fans can be installed to blow onto the PMC or to pull air away from the PMC and to blow onto the card in the next cPCI slot. Fan1 is above J1 and Fan2 above J2.

The PMC JTAG connections are routed to a header. The header is configured to for discrete connections. Please add -JTAG if you want the header installed on your cPCI2PMC.

If you have custom requirements please call or e-mail us with the details.

The cPCI bus is buffered with 10 ohm series resistors. The PCI clock is distributed with a zero delay buffer. The cPCI2PMC design is passive with no added delays to access the PMC hardware. The traces are carefully routed with proper attention paid to the impedance and reference planes to maximize compatibility with your cPCI system. The passive design of the cPCI2PMC reduces system latency.

The PCI bus is interconnected to the PMC via 64 bit 66 MHz capable layout. The slower and more narrow device will determine the interface characteristics. The M66EN selection allows the user to specify the PCI speed capabilities. M66EN is interconnected between the cPCI bus, jumper, and PMC device.

cPCI VIO is interconnected to the PMC directly. The PCI backplane will determine the bus voltage reference. The voltage select pins are not installed on the cPCI2PMC. It is for the user to properly select the PMC and cPCI motherboard for cPCI voltage level considerations. Many PMC´s are "universal" and can work with 3.3 or 5V cPCI backplanes. If you need to use a 3.3V card on a 5V backplane or vice-versa please consider the cPCIBPMC3U64ET design. The bridged implementation provides level shifting between the cPCI and PMC buses.

cPCI2PMC follows the PMC specs for maximum power consumption and heat dissipation. The power is routed from the cPCI to PMC connectors with mini-planes. Each of which is rated for more than the maximum PMC draw. 3.3V, 5V, VIO, +12V, -12V.

The individual pins on the JN4 (PN4) connector are accessible when the IO option is specified. With 3U cPCI , J2 has two definitions - in a 64 bit PCI implementation J2 has the upper A/D and control signals, and in a 32 bit PCI implemention J2 has the rear panel IO. With resistor jumpers the IO or the PCI signals can be connected to J2. Please be sure to specify -IO, -64, or blank [neither]. The routing is impedance controlled and matched length.

With the RevK and later boards cooling fans are an available option. High velocity 12V fans can be mounted to the rear or medium velocity "Zero Slot" fans can be mounted to the board. WIth the "Zero Slot" fans no extra cPCI positions are used for the fan, and the fans are legal for a PMC height and cPCI height specifications. Approximately 5 CFM per installed "Zero Slot" fan. The fans can be installed to blow onto the PMC or to pull air away from the PMC and to blow onto the card in the next cPCI slot. Fan1 is above J1 and Fan2 above J2.

The PMC JTAG connections are routed to a header. The header is configured to for discrete connections. Please add -JTAG if you want the header installed on your cPCI2PMC.

If you have custom requirements please call or e-mail us with the details.

cPCI2PMC Features

Size

3U 4HP cPCI

PMC compatible slots

1 PMC position provided. DMA capable

Clocks

cPCI bus can operate at 66 or 33 MHz. The PMC must be 66 MHz capable for 66 MHz operation to work properly. M66EN has a user switch to allow or disable 66 MHz. operation.

PMC VIO

From cPCI bus

Software Interface

passive design. Direct access to PMC defined registers etc.

Power

cPCI power rails routed to PMC for 5V, 3.3V, 12V, -12V. Mini Planes for high current capability - more than 1A per PMC pin.

Thermal

cPCI2PMC has cut-outs to support increased airflow over the PMC´s component side. Optional fan(s) with two mounting positions per PMC position are available and recommended for many applications. Industrial Temperature components.

Interrupts

INTA, INTB, INTC, INTD available. Most PMC´s use one Interrupt level [INTA].

IO Interface

PMC Bezel IO supported at cPCI bracket. Jn4 "user IO" Impedance controlled, matched length traces from Jn4 to J2 when -IO option selected.

Specification

PMC, cPCI, specification compliant

LED´s

+3V, +5V, +12V, -12V and Busmode 1.

JTAG

PMC JTAG connections are tied to a labeled header. Add -JTAG to part number for this option to be installed.

Statement of Volatility

Export Classification

EAR99, HTS:8537.10.9050

cPCI2PMC Benefits

Speed

cPCI2PMC is a passive design with low latency accesses to the installed PMC.

Price

Make use of existing PMC designs in cPCI applications without paying for the expense of a new design and layout. Quantity discounts are available.

Ease of Use

A plug and play interface to the PMC site. Plug the PMC onto cPCI2PMC, add 4 screws for retention and insert the carrier into the system.

Availability

cPCI2PMC is a popular board. We keep the default models in stock. Fans and other options can be installed for rapid delivery. Larger orders generally available with a short lead time.

Size

cPCI2PMC is a 3U 4HP design which conforms to the cPCI mechanical and electrical specifications. Eliminate mechanical interference issues.

PMC Compatibility

cPCI2PMC is PMC compliant per the PMC specification [compliant per the IEEE 1386]. All Dynamic Engineering PMC Modules are compatible with the cPCI2PMC. All other PMC Modules which are compliant with the PMC specification are compatible with cPCI2PMC

cPCI Compatibility

cPCI2PMC is cPCI compatible. cPCI2PMC is not cPCI compliant. cPCI2PMC has trace lengths slightly in excess of the maximum specified by the PCI specification. The cPCI2PMC design includes several features to minimize the effects of the longer traces. The zero delay clock buffer keeps the PCI side of the clock length within specification, and the 10 ohm series resistors help to control the AD and control signals. All cPCI bus signals are properly referenced to planes.

Single cPCI2PMC adapters can be expected to work in any PCI bus stub. If you need to operate multiple adapters per stub we recommend the cPCIBPMC3U64 is completely cPCI specification compliant. cPCI2PMC is based on the PCI2PMC which is in use in hundreds of chassis and tested in multiple backplanes. Due to the mechanical configuration a passive design will not meet all of the length specifications. Now on Release 12. Originally released in 2003. Thousands delivered.

Single cPCI2PMC adapters can be expected to work in any PCI bus stub. If you need to operate multiple adapters per stub we recommend the cPCIBPMC3U64 is completely cPCI specification compliant. cPCI2PMC is based on the PCI2PMC which is in use in hundreds of chassis and tested in multiple backplanes. Due to the mechanical configuration a passive design will not meet all of the length specifications. Now on Release 12. Originally released in 2003. Thousands delivered.

Part Number: cPCI2PMC

Ordering Options

-

cPCI2PMC - Standard Build, All models come with PMC cutout bezel. The 3U bezel mounts into the chassis and matches with the installed PMC whether rear IO or front IO, standard processing.

cPCI2PMC-IO: J2 installed and connected to Jn4 with standard rear panel IO definitions

cPCI2PMC-64: J2 installed and connected to Jn3 for upper cPCI bus signals

The "System Slot" version of cPCI2PMC has the added capability to monitor the Bus Request signals, issue bus grants, create the system reset, and drive the clock signals to the appropriate J1, J2 pins per the cPCI slot 0 specification. The base design incorporates the features. The parts associated with the slot zero capability are not installed when this option is not requested. Please note that a PrPMC can be installed into the PMC slot. The PrPMC will need to take care of bus enumeration and other slot 0 functions associated with the system processor.

cPCI2PMC-IO-SLT0: J2 installed and connected to Jn4 with standard rear panel IO definitions, plus slot 0 functions: bus arbitration, reset, clock distribution

cPCI2PMC-64-SLT0: J2 installed and connected to Jn3 for upper cPCI bus signals plus slot 0 functions: bus arbitration, reset, clock distribution

cPCI2PMC-NIO-SLT0: Standard cPCI2PMC with 32 bit PCI and slot 0 functions and no other connections to the rear panel connectors.

-JTAG: Add JTAG header to any build option

-FAN[0/1][HV][R]: Add fans in position 1 and/or 2. Fan1 is above Jn3,Jn4 and Fan2 is above Jn1,Jn2. Standard orientation is to blow onto PMC. Add "R" to each fan callout to reverse that position. Zero Slot fans have approximately 5 CFM. For an 8 CFM fan add the "-HV" designation. Please note: HV fans are mounted on the rear and will interfere with the next slot.

Examples:

-FAN12 adds 2 fans in the standard orientation - air toward PMC.

-FAN12R adds a standard orientation fan in position 1, and a reversed fan in position 2.

-FAN1R2R has both installed, and air is pulled from PMC locations.

-FAN1HVR is mounted on the rear, and pulls from the PMC in position 1.

-FAN2HV is mounted on the rear, and blows toward the PMC in position 2.

-ROHS Use ROHS processing. Standard processing is "leaded" -CC Option to add Conformal Coating

cPCI2PMC Drivers

Software Support for cPCI2PMC is not needed. cPCI2PMC is a passive design.

Please see the PMC Driver manual for the specifics of operating the installed device.

Please see the PMC Driver manual for the specifics of operating the installed device.

cPCI2PMC Manuals

Download the cPCI2PMC Manual Settings, connector maps, ordering options etc. 13p1