PCIe8LSwVPX3U

PCIe adapter for VPX

Order This Item

PCIe8LSwVPX3U Description

- Industrial Temperature

- PCIe 1-8 Lane Interface Gen3 compliant

- VPX Position with PCIe Interface Supporting Gen1-3

- SSC and NSSC support [REFCLK with SSC supplied]

- Plug and Play operation

- Local Power Supply for 3.3V, and 5V operating from system +12V

- 1/2 Length+ PCIe Card

- Bezel IO and Rear IO for installed VPX device

- Coax connectors supplied on spare clock ports to allow instrumentation of downstream port.

- 1 Year Warranty Standard. Extended Warranty Available.

- ROHS and Standard Processing Available

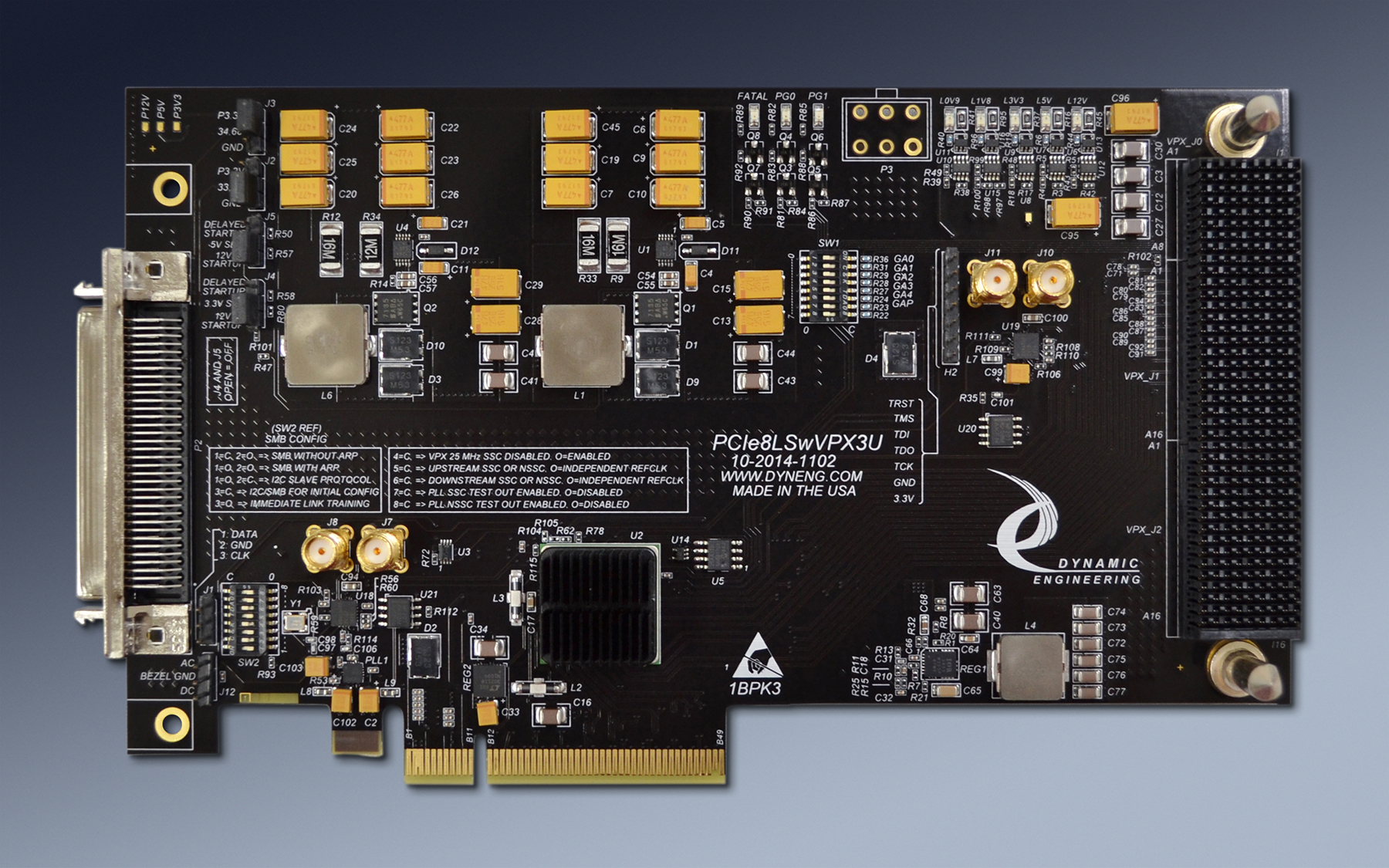

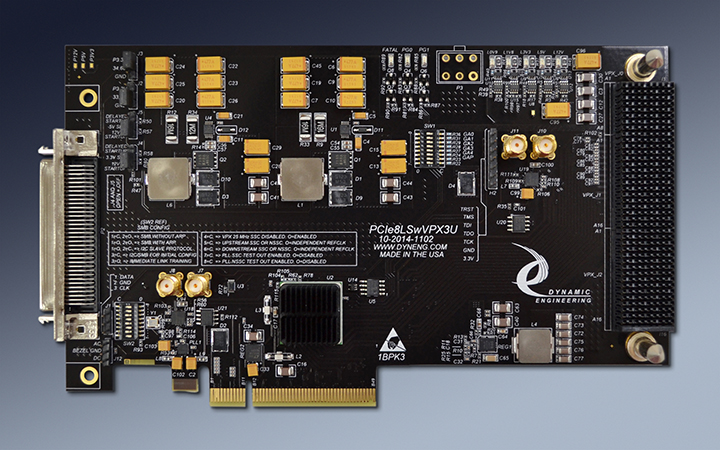

PCIe8LSwVPX3U is an 8 lane PCIe adapter with switch isolation for VPX development. The switch isolates the spread spectrum clocking found in most PC´s from the VPX port. PCIe 3.0 compliant, 1-8 lanes can be used by the installed VPX. Local power conversion for the 3.3V and 5V rails with efficient switching power supplies. Secondary power connector can be installed for high power consumption VPX cards. 15A on 3.3V and 5V rails max.[Rev 03 and later] Power monitoring circuits on the VPX and switch power rails. Status indicators for switch. Available now.

P0 on the VPX device mates with J0 on PCIe8LSwVPX3U. The connector is used for power, JTAG, and global addressing. A dip switch is supplied to allow user selection of the global address. The JTAG signals are are routed to a header on PCIe8LSwVPX3U. The 12V rail from the PCIe bus is used to generate the 3.3V and 5V supplied to P0.

The power supply designs utilize switching regulators controlling MOSFET´s. An LC filter insures clean power at the VPX device. The PCIe gold fingers are rated for 1.1A each, and a total of 5.5A on the +12V rail. 55W are available to the card after power conversion. Please note this is the combined power requirement across the +12, +5, and 3.3V power used by the VPX. In most cases 55W is sufficient. PCIe8LSwVPX3U has a standard PC Power Connector to allow additional 12V power to be added to the card. The two supplies are DIODE coupled. In some cases the 12V supply on the backplane will not be adequately routed by the PC causing voltage sag on the 12V. If this occurs use the cable connector to compensate. The power supplies include the bulk capacitance to properly bipass the FET´s and post conversion voltage rails. In addition the VPX connectors are bipassed with a 470 uF capacitor. The power supplies are checked with voltage monitor circuits. The LED´s are not illuminated unless the voltage is within the defined range.

The switch on PCIe8LSwVPX3U is interconnected with the PCIe lanes from the gold finger connections. Matched length, 100 ohm differential pair routing techniques are employed to allow for trouble free operation. Your PC can use spread spectrum clocking, and the built in switch isolates the spread spectrum upstream port from the down stream VPX side. New with Revision B, PCIe8LSwVPX3U supports both SSC and NSSC for the down steam port [VPX side]. With switch settings the clocking reference for the VPX interface can be updated to use a high precision 100 MHz independent clock or the REFCLK - 25 MHz with SSC.

We use the VPX8LXMC3U carrier to allow an XMC-Parallel-TTL to be installed onto the PCIe8LSwVPX3U via the adapter. The carrier can use REFCLK, or a local high precision reference to support the PCIe links. We use the rear IO from the XMC to test the path through to the SCSI connector at the bezel of PCIe8LSwVPX3U.

The Rear IO (P2) connector is carefuly routed to a 68 pin SCSI connector. 100 ohm differential routing with matched length traces. We recommend using our SCSI cable and the HDEterm68 breakout block with the SCSI connector.

Alignment pins are supplied to make sure of correct installation. The VPX installed will be perpendicular to the PCIe8LSwVPX3U with the component side to the right [relative to the photo above]. The VPX connector is located on the right hand side of the PCIe8LSwVPX3U in a position to allow a PCI or PCIe 1/2 length card to be used in the slot in front of the PCIe8LSwVPX3U.

LED´s are provided for 3 switch status signals. FATAL is provided to indicate a fault with the switch, PG0 and PG1 indicate the level of link activity on Port 0 and Port 1. A steady LED indicates PCIe 3.0 operation, flashing indicates PCIe 2.0 or PCIe 1.0 depending on the rate of flashing, and off indicates an unused port. Port 0 is the upstream port and in a new PC will likely show a steady LED for PCIe 3.0 operation. Port1 is the downstream port and after enumeration with the installed VPX will show the speed achieved on that port. The Switch allows for different upstream and downstream speeds. The switch has internal memory which will help with system traffic levels when connecting to a lower speed secondary port. Please see the manual for more information.

P0 on the VPX device mates with J0 on PCIe8LSwVPX3U. The connector is used for power, JTAG, and global addressing. A dip switch is supplied to allow user selection of the global address. The JTAG signals are are routed to a header on PCIe8LSwVPX3U. The 12V rail from the PCIe bus is used to generate the 3.3V and 5V supplied to P0.

The power supply designs utilize switching regulators controlling MOSFET´s. An LC filter insures clean power at the VPX device. The PCIe gold fingers are rated for 1.1A each, and a total of 5.5A on the +12V rail. 55W are available to the card after power conversion. Please note this is the combined power requirement across the +12, +5, and 3.3V power used by the VPX. In most cases 55W is sufficient. PCIe8LSwVPX3U has a standard PC Power Connector to allow additional 12V power to be added to the card. The two supplies are DIODE coupled. In some cases the 12V supply on the backplane will not be adequately routed by the PC causing voltage sag on the 12V. If this occurs use the cable connector to compensate. The power supplies include the bulk capacitance to properly bipass the FET´s and post conversion voltage rails. In addition the VPX connectors are bipassed with a 470 uF capacitor. The power supplies are checked with voltage monitor circuits. The LED´s are not illuminated unless the voltage is within the defined range.

The switch on PCIe8LSwVPX3U is interconnected with the PCIe lanes from the gold finger connections. Matched length, 100 ohm differential pair routing techniques are employed to allow for trouble free operation. Your PC can use spread spectrum clocking, and the built in switch isolates the spread spectrum upstream port from the down stream VPX side. New with Revision B, PCIe8LSwVPX3U supports both SSC and NSSC for the down steam port [VPX side]. With switch settings the clocking reference for the VPX interface can be updated to use a high precision 100 MHz independent clock or the REFCLK - 25 MHz with SSC.

We use the VPX8LXMC3U carrier to allow an XMC-Parallel-TTL to be installed onto the PCIe8LSwVPX3U via the adapter. The carrier can use REFCLK, or a local high precision reference to support the PCIe links. We use the rear IO from the XMC to test the path through to the SCSI connector at the bezel of PCIe8LSwVPX3U.

The Rear IO (P2) connector is carefuly routed to a 68 pin SCSI connector. 100 ohm differential routing with matched length traces. We recommend using our SCSI cable and the HDEterm68 breakout block with the SCSI connector.

Alignment pins are supplied to make sure of correct installation. The VPX installed will be perpendicular to the PCIe8LSwVPX3U with the component side to the right [relative to the photo above]. The VPX connector is located on the right hand side of the PCIe8LSwVPX3U in a position to allow a PCI or PCIe 1/2 length card to be used in the slot in front of the PCIe8LSwVPX3U.

LED´s are provided for 3 switch status signals. FATAL is provided to indicate a fault with the switch, PG0 and PG1 indicate the level of link activity on Port 0 and Port 1. A steady LED indicates PCIe 3.0 operation, flashing indicates PCIe 2.0 or PCIe 1.0 depending on the rate of flashing, and off indicates an unused port. Port 0 is the upstream port and in a new PC will likely show a steady LED for PCIe 3.0 operation. Port1 is the downstream port and after enumeration with the installed VPX will show the speed achieved on that port. The Switch allows for different upstream and downstream speeds. The switch has internal memory which will help with system traffic levels when connecting to a lower speed secondary port. Please see the manual for more information.

PCIe8LSwVPX3U Features

Size

1/2 size+. 8 lane design with matched length impedance controlled routing. 1-8 lanes operational depending on motherboard and VPX installed

VPX compatible position

1 VPX 3U Slot provided.

Clocks

Gen1 - Gen3 compatible.

Global Addressing

Supported with a user DIPSWITCH

Software Interface

Transparent design with no SW requirement. Switch is highly configurable should the user want to make adjustments via I2C/ EEPROM. VPX register definitions as defined by installed hardware.

Power

3.3V and 5V power supplies capable of up to 9.5A continuous without additional cooling in lab environment. The max FET temperature was below 100C. The max junction temperature of the FET is 150C. We used a case temperature limit of 100C to be conservative. A

midpointof 7.44A on 5V and 6.6A on 3.3V produced 65.8C on the 5V FET with no cooling [3.3V FET was 57.6C]. We can estimate that the card can handle the given load up to 50C with some margin. With lighter loads higher temperatures can be achieved without cooling. With cooling higher loads can be achieved at higher temperatures.

Interrupts

PCIe MSI interrupt scheme is supported

IO Interface

Front Bezel IO supported at VPX bracket. P2 "user IO" supported with SCSI connector mouted to Bezel on PCIe2VPX3UX4. Differential Impedance controlled matched length traces from P2 to SCSI connector.

Specification

VPX[VITA 46], PCIe specification compliant

LED´s

.9V, 1.8V, +3V, +5V, 12V [with voltage monitoring] plus FATAL, PORT_GOOD0 and PORT_GOOD1

JTAG

VPX JTAG connections are tied to a labeled header. Add -JTAG to part number for this option to be installed.

Statement of Volatility

PCIe8LSwVPX3U Benefits

Speed

PCIe8LSwVPX3U offers Gen1-3 speeds with 1-8 lanes. Use current and future VPX´s

Price

Make use of existing PC based debugging tools to speed your integration. We use with Visual Studio to allow for compiling and single stepping through our designs. We find this configuration very efficient for solving HW issues in new designs. Mount your VPX into a PC and have full access to components and debugging SW. Quantity discounts are available.

Ease of Use

PCIe8LSwVPX3U is easy to use. A plug and play interface to the VPX site. A switch isolated design with minimal settings. The defaults will likely work for you. You may want to use with a motherboard not installed into a chassis for total freedom. We use this set-up to have full access to the hardware you are developing.

Availability

PCIe8LSwVPX3U is generally available from stock. Send in your order for rapid delivery.

Size

PCIe8LSwVPX3U is a half size+ PCIe board which conforms to the PCIe mechanical and electrical specifications. The VPX connectors are located to clear a 1/2 length PCIe card to allow adjacent slots to be used.

VPX Compatibility

PCIe8LSwVPX3U is VPX compliant per the VITA 46 specification. All Dynamic Engineering 3U VPX Modules are compatible with the PCIe8LSwVPX3U. All other VPX 3U Modules which are compliant with the VITA 46 specification are compatible with the PCIe8LSwVPX3U.

PCIe Compatibility

PCIe8LSwVPX3U is PCI Express compliant. PCIe8LSwVPX3U can be expected to work in any PCIe compliant backplane. PCIe8LSwVPX3U has been tested in multiple backplanes. 8 or more lane connector slots support the PCIe8LSwVPX3U.

Part Number: PCIe8LSwVPX3U

Ordering Options

- PCIe8LSwVPX3U Standard board - for a base version (PCIe8LSwVPX3U) and standard processing

- -ROHS Use ROHS processing. Standard processing is ""leaded"

- -CC Option to add Conformal Coating

- -NC Order to receive a PCIe8LSwVPX3U with no SCSI installed.

- -JTAG Order to receive a PCIe8LSwVPX3U with the JTAG header installed

- -AP Order to receive a PCIe8LSwVPX3U with the Alternate high power connector installed for supplemental power. PC standard 2 row by 3 power cable receptical. Pins1,2,3 = +12V. Pins 4,5,6 = GND. Please note that the standard card without the -AP option will work in most situations. Many VPX´s fit within the "gold finger" power budget.

If you are unsure of your power requirements, we recommend ordering with a Power Connector installed to support your future development, and eliminate the need to install at a later date.

PCIe8LSwVPX3U Drivers

Software Support for PCIe8LSwVPX3U is not needed. PCIe8LSwVPX3U is a passive card, the drivers and application SW associated with the XMC will not need changing based on using this carrier.

Please see the XMC Driver manual for the specifics of operating the installed device.

Please see the XMC Driver manual for the specifics of operating the installed device.

PCIe8LSwVPX3U Manuals

PCIe8LSwVPX3U Hardware Design Manual Main product manual with example use, pinouts, specifications and more.