| Size |

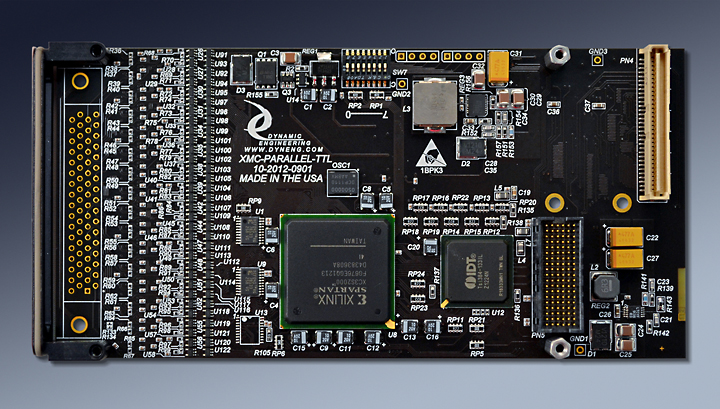

Single wide XMC.

|

| |

|

| Parallel Interface |

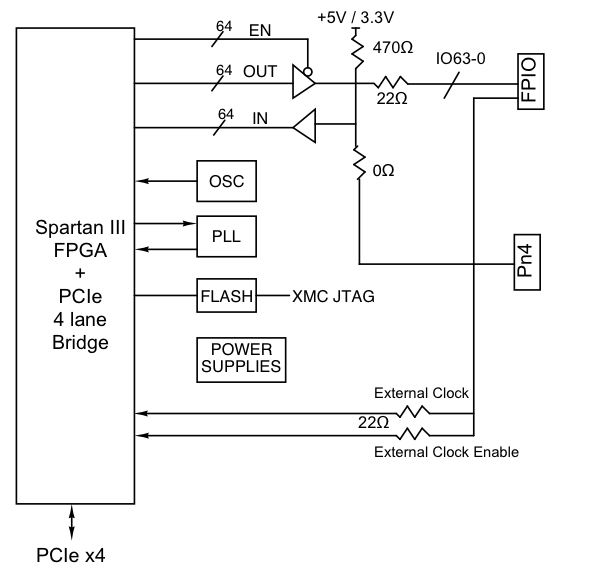

64 independent channels. The pull-ups can be referenced to 3.3V or 5V. Front Panel [Bezel], Rear IO [Pn4] or Both ports available. Unused ports isolated with resistors for "zero bus stub". Matched IO within 1/1000 inch for on-board traces to front and rear.

|

| |

|

| Pull-up Resistor |

470 standard, 1K, 4.7K available.

|

| |

|

| Sink Current |

64+ mA per channel

|

| |

|

| Cable interface |

Industry standard SCSI III front panel IO and Pn4 backplane connection.

|

| |

|

| Software Interface |

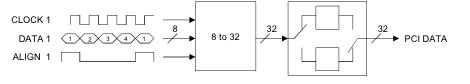

32 bit registers mapped to the 64 IO channels. Read-back of channel control registers and input registers. Read-write of control registers for card configuration.

|

| |

|

| Interrupts |

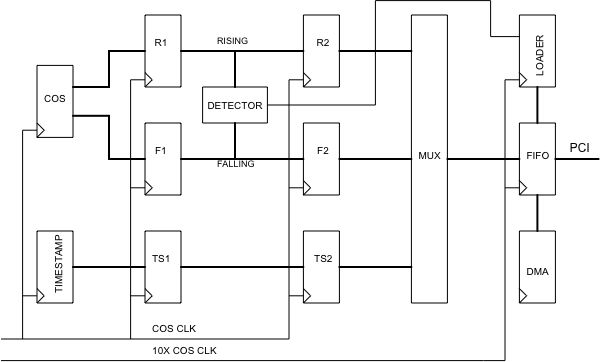

All IO Channels can be programmed to cause interrupts. Each channel is programmable to be masked, rising, falling, both [COS].

|

| |

|

| Power Requirement |

XMC standard. VPWR can be +5 or +12V.

|

| |

|

| Protection |

The isolation resistors standard is 0 ohms to Pn4 and 22 ohms to Bezel. Resistive coupling for current limiting and ESD protection.

|

| |

|

| COS Clock |

Input registers are programmable to capture data with the COS clk. SW can select 33 MHz, external or Oscillator as the source for clock. A programmable divider [12 bit] allows a wide range of sampling frequencies to be selected. Some versions use the PLL for the COS clock definition.

|

| |

|

| Custom |

All bits are routed through the FPGA to allow for custom state-machine implementations. FIFO and Dual Port RAM can be implemented. See custom models below.

|

| Speed |

XMC-Parallel-TTL is a software controlled HW interface. As fast as the PCIe interface can push the data across, the outputs can change. With the Windows® driver several accesses per microsecond can be achieved. Your time to market will be shortened by the easy to use interface, flexibility in design, and off-the-shelf availability. With DMA enabled and FIFO´s instantiated even faster transfers can occur.

|

| |

|

| Price |

XMC-Parallel-TTL has an attractive price, and low integration cost for a low system cost. XMC Parallel TTL has an associated PIM and PIM Carrier which can lead to further savings in cPCI environments.

|

| |

|

| Ease of Use |

XMC-Parallel-TTL is easy to use. A point and shoot user interface to the IO. Please download the manual and see for yourself. The engineering kit provides a good starting point for a new user. 64 bits of user defined IO.

|

| |

|

| Availability |

XMC-Parallel-TTL is a popular board. We keep XMC-Parallel-TTL in stock. Send in your order and in most cases have your hardware the next day - delivered to you via FedEx. Custom versions can be dialed in quickly as well as customer requested VHDL features. Consider using scheduling on your next order. Available now.

|

| |

|

| Size |

XMC-Parallel-TTL is a standard single wide XMC [single slot] board which conforms to the XMC mechanical and electrical specifications. Eliminate mechanical interference issues.

|

| |

|

| XMC Compatibility |

XMC-Parallel-TTL is XMC compliant per the VITA specification. |

| |

|

| PCIe Compatibility |

XMC-Parallel-TTL is PCIe compliant. You can develop with a PCIe to XMC adapter - PCIe8LXMCX1 or PCIe8lXMCX2 etc.. |