PCIe Altera Cyclone IV

PCIe User Configurable Logic with 40 LVDS or RS-485, and 12 TTL IO

Order This Item

PCIeAlteraCycloneIV Description

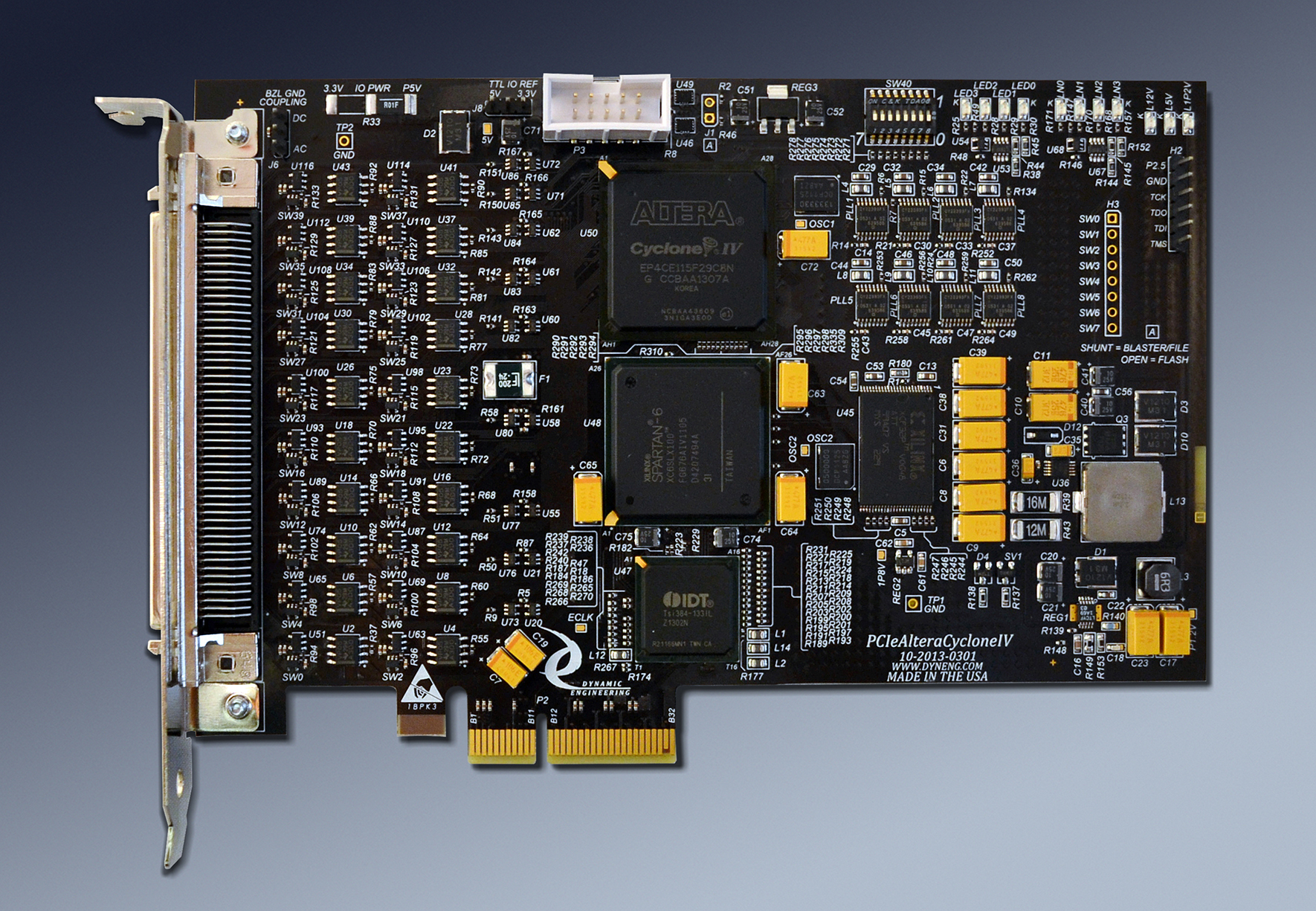

- Altera Cyclone IV FPGA for user program, with local FLASH and on-the-fly loading

- 40 Differential IO - 485, LVDS or MIXED

- 12 TTL IO

- 24 PLL clocks

- 8 Full Duplex Ports between Controller and User FPGA

- 16 channel DMA

- PCIe 1-4 Lane Interface

- Plug and Play operation

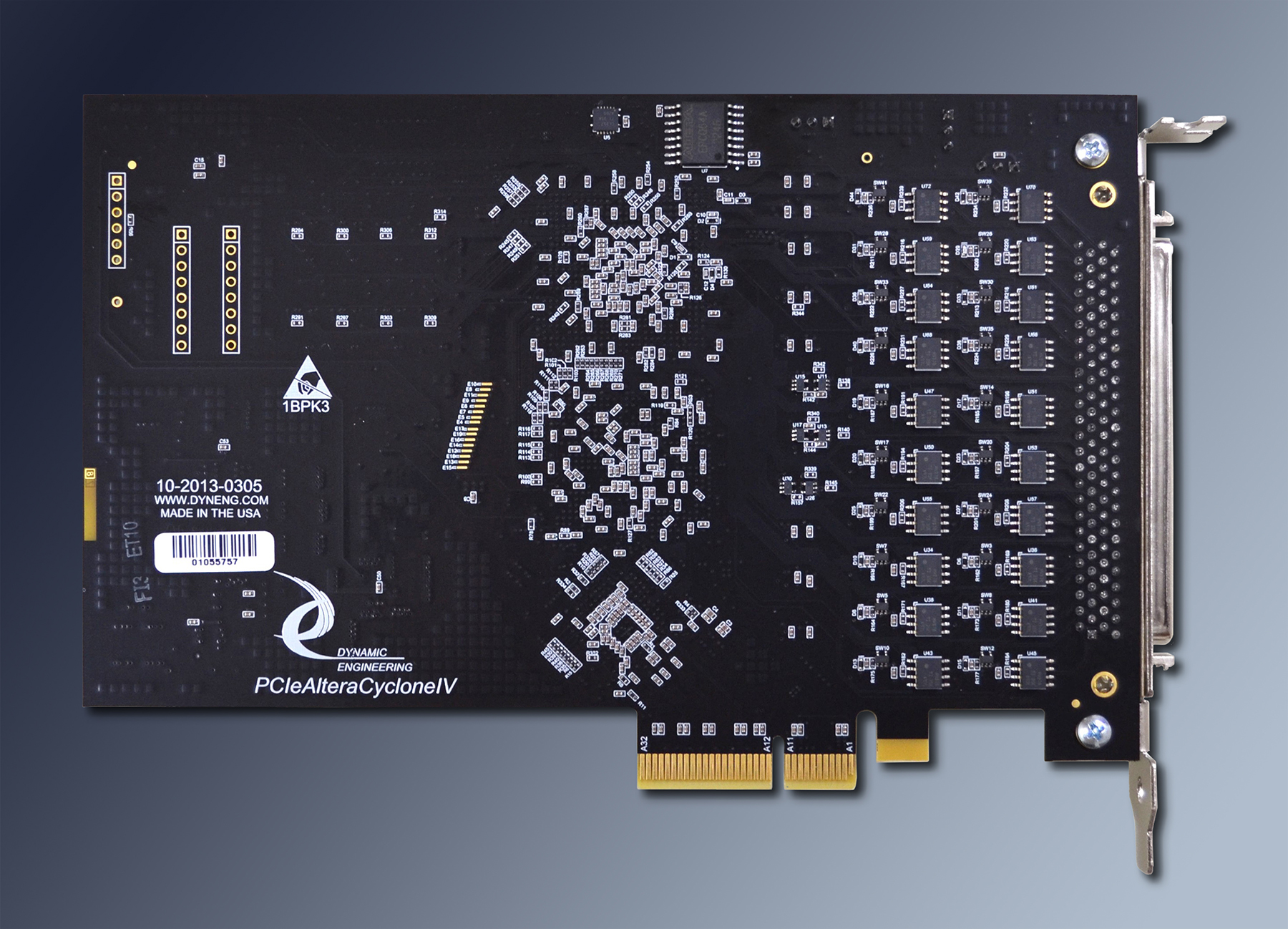

- 1/2 Length PCIe Card

- 1 Year Warranty Standard. Extended Warranty Available.

- ROHS and Standard Processing Available

User Configurable Logic - PCIe Altera Cyclone IV 485/LVDS comes with everything you need to load your Altera program into the Cyclone IV. Fantastic for development, simulation, special purpose interfaces, multiple serial and / or parallel channels. FLASH and on-the-fly reloading for configurable and reconfigurable logic implementations.

PCIe compatible PCIeAlteraCycloneIV-485/LVDS design is for the advanced user who wants to implement their own Altera design or requires updatable logic. PCIeAlteraCycloneIV makes the implementation, and use of the Cyclone IV easy.

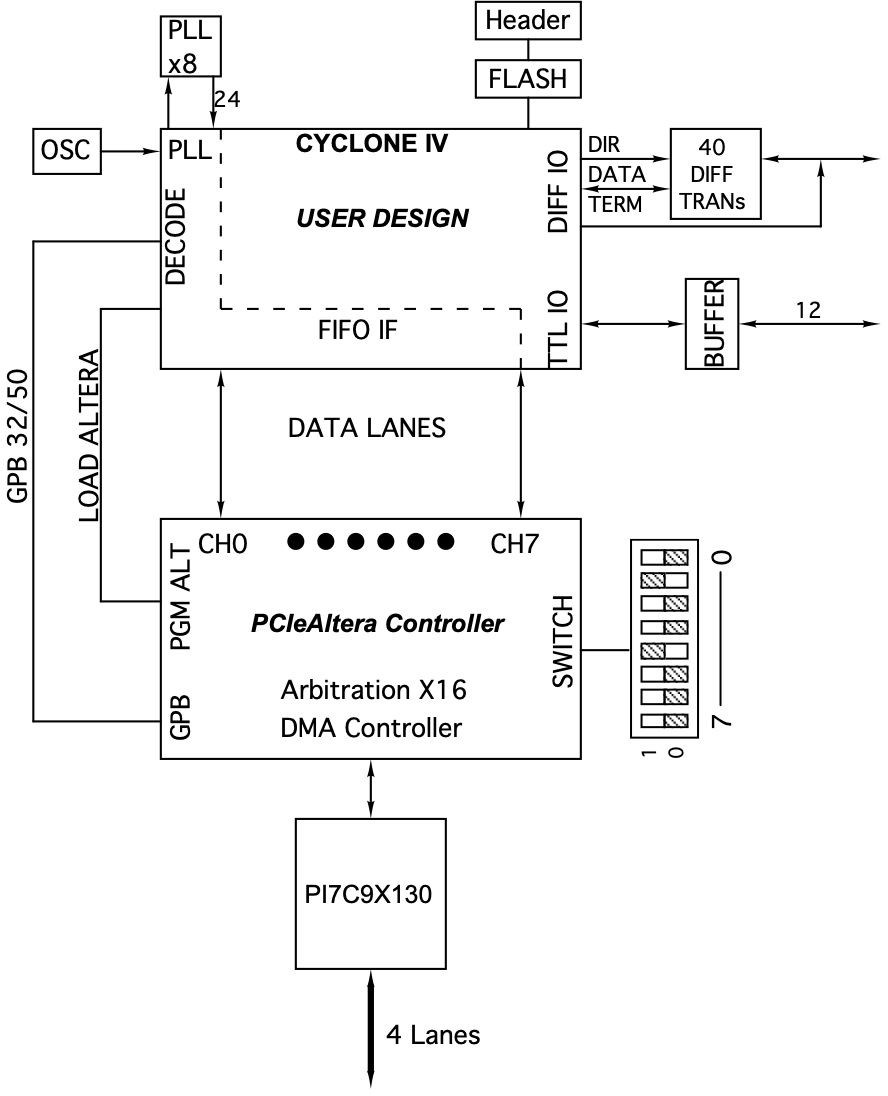

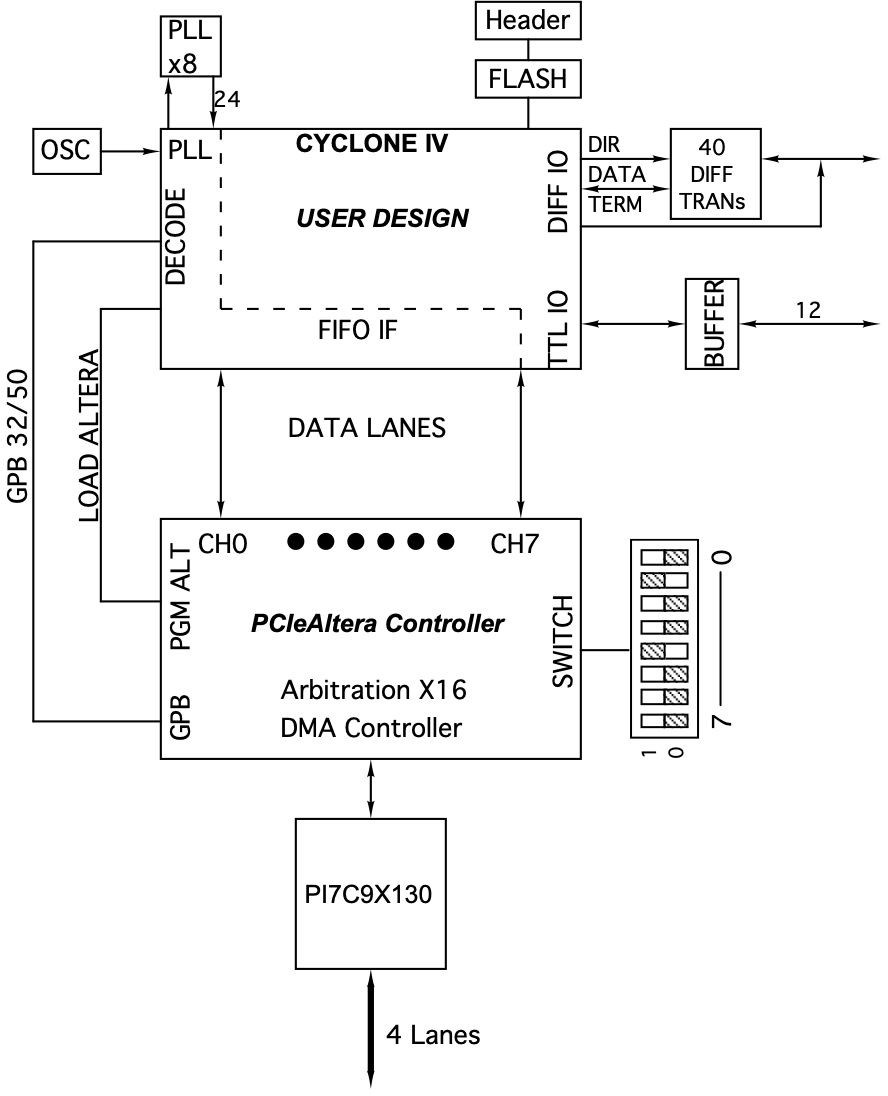

The design comes with the basic features built in and the specific features ready for you. The PCIe-Altera Controller takes care of the PCIe interface for initial loading of the Altera Cyclone IV, and DMA transfer of data into and out of the FIFOs. The Altera FPGA controls 40 programmable RS-485 or LVDS transceivers and 12 TTL IO. Each of the RS-485 or LVDS channels is programmable for direction, termination and function. The IO can be mixed too. The 12 TTL IO can be inputs or outputs. Eight Cypress 22393 PLLs support the FPGA with 24 programmable clock references. The only thing missing is your input in the form of a coprocessor, reconfigurable logic, state-machine, simulated system, asynchronous or synchronous data processing etc.

Software [Windows and Linux] to load the Altera, access the hardware, and run diagnostics is available as well as a reference design for the Altera Cyclone IV which controls the byte lanes, IO, and PLLs. The drivers come with calls for the standard features plus a generic R/W interface to allow for any user update without needing driver modifications. Many of the reference software files use the generic IO control to show how this is done. We provide a plug ´n play set-up along with our ATP software to give you a running start at your design.

PI7C9X130 is used to bridge between the 4 lane PCIe interface and the PCIe-Altera Controller [Xilinx Spartan 6 FPGA]. Together the bridge and Spartan 6 are used to move data to the Altera for output channels, and to move data to the host for input channels. 8 input and 8 output FIFOs are provided to support 8 bi-directional channels. The intermediate FIFOs are byte wide and operate at 66 MHz between the Spartan 6 and Cyclone IV. Each of the data paths has its own DMA controller and local arbitration to move data from the Altera through the Xilinx to the the PCIe lanes or vice-versa. In addition, a control bus is provided - 32 data, 12 address, 33 MHz to provide a method of programming registers or memory within the User Design. An interrupt request from the Altera through the Xilinx is provided.

IO is accomplished via RS-485 or LVDS transceivers or TTL buffers. The RS-485 transceivers are rated for 40 MHz. The LVDS is rated for 200 MHz. Each transceiver can be controlled for direction and termination. The TTL IO is implemented with ´125 open drain drivers with on-board pull-ups. The input direction is buffered with a receiver to protect the Altera and to provide level shifting between the 5V IO and the 3.3V Altera IO. The D100 [ SCSI II 100 pin connector ] provides an easy to interconnect cabling system. The pinouts are consistent with the industry standard differential pairings. The HDEterm100 supports the D100 with a cable to terminal strip conversion.

An 8 position dip switch is provided. The switch is read through the Controller FPGA. The switch can be used to distinguish multiple PCIeAlteraCycloneIV boards in the same system or for other user determined purposes.

LEDs are provided. 4 are controlled via the Altera and the user design. Others are provided to show the power suppies are within tolerance. The LEDs can be used for debugging or for system status etc.

We can do the design implementation for you, and provide the design files to you for long term support. If you need the features of the PCIeAlteraCyclone IV and prefer to have someone else do the programming, please contact us with your requirements.

PCIe compatible PCIeAlteraCycloneIV-485/LVDS design is for the advanced user who wants to implement their own Altera design or requires updatable logic. PCIeAlteraCycloneIV makes the implementation, and use of the Cyclone IV easy.

The design comes with the basic features built in and the specific features ready for you. The PCIe-Altera Controller takes care of the PCIe interface for initial loading of the Altera Cyclone IV, and DMA transfer of data into and out of the FIFOs. The Altera FPGA controls 40 programmable RS-485 or LVDS transceivers and 12 TTL IO. Each of the RS-485 or LVDS channels is programmable for direction, termination and function. The IO can be mixed too. The 12 TTL IO can be inputs or outputs. Eight Cypress 22393 PLLs support the FPGA with 24 programmable clock references. The only thing missing is your input in the form of a coprocessor, reconfigurable logic, state-machine, simulated system, asynchronous or synchronous data processing etc.

Software [Windows and Linux] to load the Altera, access the hardware, and run diagnostics is available as well as a reference design for the Altera Cyclone IV which controls the byte lanes, IO, and PLLs. The drivers come with calls for the standard features plus a generic R/W interface to allow for any user update without needing driver modifications. Many of the reference software files use the generic IO control to show how this is done. We provide a plug ´n play set-up along with our ATP software to give you a running start at your design.

PI7C9X130 is used to bridge between the 4 lane PCIe interface and the PCIe-Altera Controller [Xilinx Spartan 6 FPGA]. Together the bridge and Spartan 6 are used to move data to the Altera for output channels, and to move data to the host for input channels. 8 input and 8 output FIFOs are provided to support 8 bi-directional channels. The intermediate FIFOs are byte wide and operate at 66 MHz between the Spartan 6 and Cyclone IV. Each of the data paths has its own DMA controller and local arbitration to move data from the Altera through the Xilinx to the the PCIe lanes or vice-versa. In addition, a control bus is provided - 32 data, 12 address, 33 MHz to provide a method of programming registers or memory within the User Design. An interrupt request from the Altera through the Xilinx is provided.

IO is accomplished via RS-485 or LVDS transceivers or TTL buffers. The RS-485 transceivers are rated for 40 MHz. The LVDS is rated for 200 MHz. Each transceiver can be controlled for direction and termination. The TTL IO is implemented with ´125 open drain drivers with on-board pull-ups. The input direction is buffered with a receiver to protect the Altera and to provide level shifting between the 5V IO and the 3.3V Altera IO. The D100 [ SCSI II 100 pin connector ] provides an easy to interconnect cabling system. The pinouts are consistent with the industry standard differential pairings. The HDEterm100 supports the D100 with a cable to terminal strip conversion.

An 8 position dip switch is provided. The switch is read through the Controller FPGA. The switch can be used to distinguish multiple PCIeAlteraCycloneIV boards in the same system or for other user determined purposes.

LEDs are provided. 4 are controlled via the Altera and the user design. Others are provided to show the power suppies are within tolerance. The LEDs can be used for debugging or for system status etc.

We can do the design implementation for you, and provide the design files to you for long term support. If you need the features of the PCIeAlteraCyclone IV and prefer to have someone else do the programming, please contact us with your requirements.

PCIeAlteraCycloneIV Features

Size

Small size PCIe card.

Altera

Cyclone IV 115 EP4CE115F29(I,C)(7,8) standard.

Clocks

133.333 MHz reference oscillator and 33 MHz. reference clock connected to Altera. 8 Cypress 22393 PLLs are controlled by the Altera. Each with 3 programmable clocks. Each PLL has a separate reference. 12 PLL clock inputs to the Altera are routed to Altera Clock Inputs.

PCIe Bus

4 lanes interconnected to the Bridge. 1-4 lane operation. 4+ lane connector compatible.

Software Interface

Industry Standard Bridge register definitions. The bridge does not require any user set-up. PMC register definitions as defined by installed hardware. For superior DMA perfomance some Bridge settings should be enhanced. Dynamic Engineering Drivers [Linux and Windows] have this feature. Ask and we can share the registers, offsets and new values.

Power Requirement

+12V and 3.3 from PCIe interface, other local voltages converted on card.

IO

40 - 40 MHz. capable RS-485 or 40-200 MHz LVDS or 20 of each type plus 12 TTL IO are provided. Additional TTL IO can be provided by removing some Differential IO.

Software Interface

Control registers are read-writeable. Mechanism to download Altera implementation Iis provided in HW and reference SW.

Cable interface

D100 connector provided with differential pinouts Differential, Impedance controlled, matched length traces.

Specification

PCIe specification compliant

LEDs

4 user LEDs plus Lane Activity [PCIe] and Power Good from voltage monitor circuits.

DIP switch

An 8 position switch is available to allow for configuration control or to facilitate debugging

Statement of Volatility

Reliability

TBD

PCIeAlteraCycloneIV Benefits

Speed

DMA access supported with 16 separate DMA engines. Each port can operate with a separate thread. 40 MHz RS-485 or 200 MHz LVDS. 16 rate matching FIFOs for full support of 8 bi-directional serial or parallel data channels. Altera EP4CE115F29I8. [larger parts and different speed grades are available by special order] The hardware can sustain high speed operation on multiple IO channels.

Price

PCIeAlteraCycloneIV-485/LVDS is a generic board which can be shaped for your needs. It is off-the-shelf and much lower cost than developing your own PCB, loader software etc. Quantity discounts are available making it the way to go for your production requirements too. Once your implementation is "nailed" we can do a specific version for you with minimized or expanded features.

Ease of Use

PCIeAlteraCycloneIV-485/LVDS is easy to use. Just plug in and download your implementation. The engineering kit comes with support to load the Altera, reference VHDL for the Altera, and software to support your design plus break-out box and cable.

Availability

PCIeAlteraCycloneIV-485/LVDS is available either off-the-shelf or with a short lead time for the commercial version. The -ET version may have some lead time depending on device availability. Dynamic Engineering has full SMT manufacturing capability for better support and faster delivery.

Size

PCIeAlteraCycloneIV-485/LVDS is a half size PCIe board which conforms to the PCIe mechanical and electrical specifications. Can be used in 4 lane or larger PCIe connectors.

PCIe Compatibility

PCIeAlteraCycloneIV is PCIe compliant. PCIeAlteraCycloneIV can be expected to work in any PCIe compliant backplane with 4+ lane connectors and 1/2 or full length card positions. PCIeAlteraCycloneIV has been tested in multiple backplanes.

Part Number: PCIeAlteraCycloneIV

Ordering Options

- PCIeAlteraCycloneIV Add the following options to the base part number to build your ordering option

- -485 IO version

- -LVDS IO version

- -MIXED Mix the LVDS and 485 IO. 20 LVDS and 20 485 IO. 0-19 are LVDS, 20-39 are 485. For other options please contact the factory to provide the channel counts that you require. A new -# will be created for your version.

- -V Alternate verticle connector installed for internal wiring

- -ET Upgrade PCIeAlteraCycloneIV to Industrial temperature. Minimum quantities may apply to this option.

- -CC Add Conformal Coating

- -ROHS Change to ROHS compliant processing

Engineering Kits

PCIeAlteraCycloneIV is supported with Software[Driver and sample application ] Windows , and Linux are options. The drivers include a general purpose call for the GPB bus allowing the user to completely remap the Altera design [should they want to] without needing a new driver. Existing driver and reference SW for PCIeAlteraCycloneIV are included with your purchase of PCIeAlteraCycloneIV. Software products are supplied AS-IS. For integration support with your project Dynamic Engineering offers Technical Support Packages.

Other recommended accessories include HDETerm100-ENG, and HDECable100. HDEcabl100 mates with the D100 connector on PCIeAlteraCycloneIV and provides a shielded twisted pair connection to your electronics. The signals can be broken out with HDEterm100 or a custom cable can be designed and manufactured for you. Please contact Dynamic Engineering with your cable requirements.

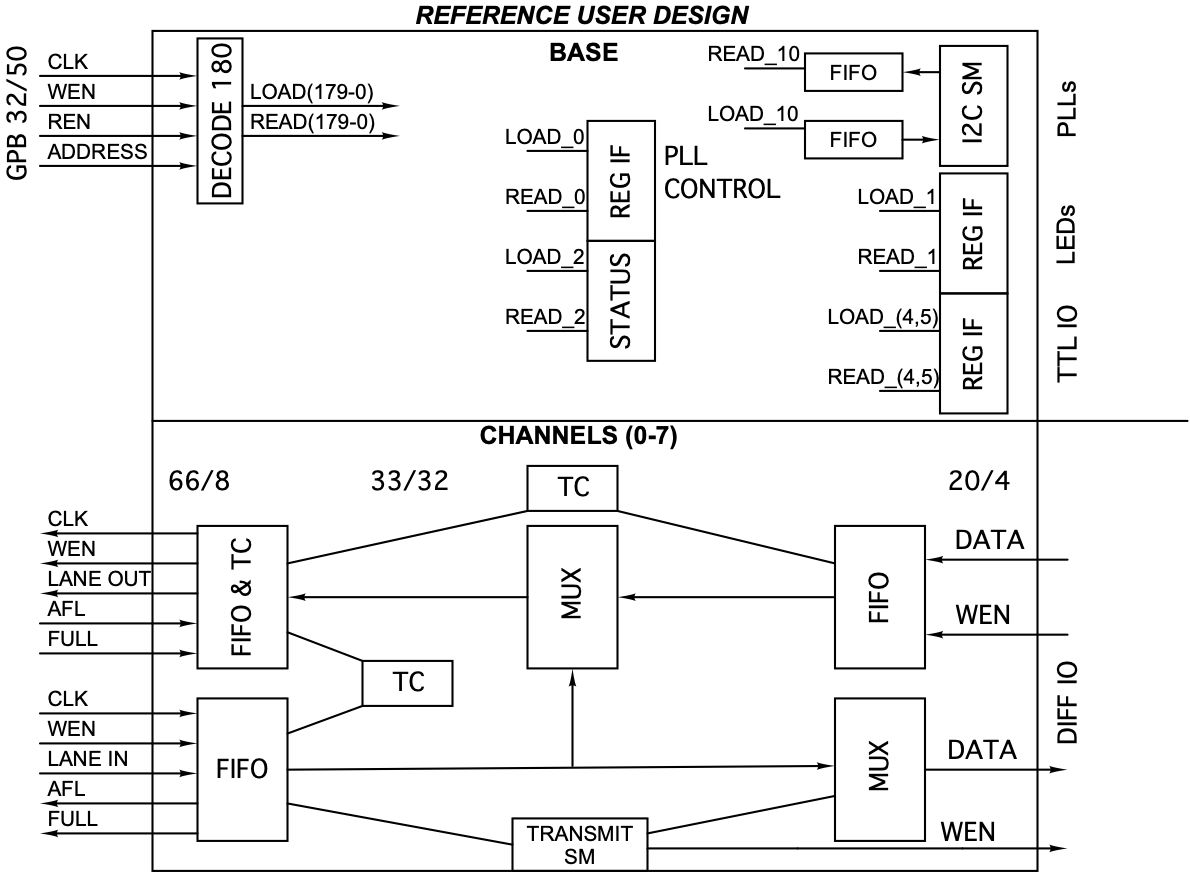

Block diagram of VHDL design included with Hardware Support Engineering Kit.

The VHDL source code for the design shown in the block diagram ispart of the Hardware Support Engineering Kit. The design is a good starting point for many user designs. The design includes all of the basics that you will need : Bus interface to GPB, memory interface to FIFOs, PLL, TTL, and Differential IO, termination and direction control. Dynamic Engineering uses this design along with the driver and Userap.exe program [source for Userap.exe included in Software support Engineering kit] to test the PCIeAlteraCycloneIV design.

PCIeAlteraCycloneIV Drivers

Software Support for PCIeAlteraCycloneIV is available for Linux and Windows. Each package comes with the driver to connect the OS to the HW and a reference application to demostrate how to use driver. The driver packages have calls to support all of the features of the design including DMA, GPB, PLLs, IO, loading and reloading the FPGA etc. The reference SW has examples showing how to use the various features. Some tests use HDEterm100 plus the IO cable to do loop-back. The sw application can be used as a reference or as as basis for your design.

PCIeAlteraCycloneIV Manuals

Download the PCIeAlteraCycloneIV HW Manual in PDF format.

Download the PCIeAlteraCycloneIV Linux Manual Rev 1.0.0

Download the PCIeAlteraCycloneIV Win10 Manual Rev 1p1

Certificate of Volatility in PDF format.

Download the PCIeAlteraCycloneIV Linux Manual Rev 1.0.0

Download the PCIeAlteraCycloneIV Win10 Manual Rev 1p1

Certificate of Volatility in PDF format.