PC/104p-BiSerial

PCI-104 and PC/104p Compatible Bi-Directional Serial Data Interface

Front View - shown with development header installed

Rear View- shown with development header installed

| Standard PC/104p |

|

| |

|

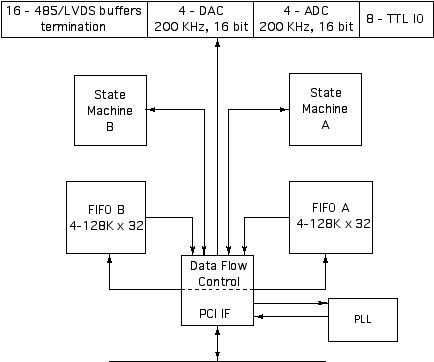

| 40 MHz RS485 signaling supported. LVDS transceivers rated at 200 MHz. Xilinx may limit the top rate, 200 KHz ADC, 200 KHz DAC, TTL is Xilinx driven. |

|

| |

|

| PLL [Cypress 22393], PCI, OSC, External clock sources are available for use |

|

| |

|

| Standard 33 MHz. operation |

|

| Standard 32 bit operation supported. |

|

| Registers are read-writeable. Transmit and Receive functions separated. | |

| Transmit and Receive state-machines, FIFO Programmable almost empty [transmit] and programmable almost full [receive] have programmable interrupts. Status can be polled for non-interrupt driven operation as well. |

|

| |

|

| 16 RS-485 / RS-422 compatible IO are provided. Any combination of transmit or receive channels can be created. Programmable termination. LVDS IO are available on all channels. Up to 4 DAC channels and/or 4 ADC channels can be added. Each channel can operate at 200 KHz and has a 16 bit resolution. 8 TTL IO are provided. |

|

| |

|

| The IO is available via the 50 pin right angle header. The differential IO is properly routed with controlled spacing and matched lengths on each of the pairs. |

|

| |

|

| The -IO version of the PC/104p BiSerial has support for Data, Clock and Strobe. Custom programmed interfaces are available with other options. |

|

| +5 only. 3.3 and 2.5 converted with on-board regulator. |

|

| Separate FIFOs are provided for both channels. 4K x 32 is standard. 8K, 16K, 32K, 64K, and 128K x 32 are available. |

|

| The PC/104p BiSerial is optimized for serial interfacing requirements. The FIFO memories and programmable interrupts off-load the CPU from most of the management other implementations require. The FIFO access is optimized for the PCI bus further reducing overhead by speeding up the data transfer. On the IO side the PMC BiSerial has independent channel functions. Both channels can operate at maximum rate in parallel. |

|

| |

|

| The PC/104p BiSerial is easily programmed to implement new functions. Many previously implemented "custom designs" are available too. Without the costs of schematic level design, layout, debugging etc. a modified BiSerial will represent a large cost savings in your budget. |

|

| |

|

| The PC/104p BiSerial is easy to use. Point and shoot - just fill the FIFO and set the start bit to get your custom protocol transmitting. Built in loop-back capabilities and engineering kits help with integration into your system. We can write a custom Windows driver for you. |

|

| |

|

| Dynamic Engineering works to keep the PC/104p BiSerial in stock. Send in your order and in most cases have your hardware the next day. With a custom design a 1-2 week design period is usually required. We can support immediately with the -IO version then send updated PROMs later to help get your project going - right away. This design is currently in layout. |

|

| |

|

| The PC/104p BiSerial is a standard single width PC/104p card and meets the PC/104p mechanical specifications. The PC/104p BiSerial can be used in all PC/104p slots. |

|

| |

|

| The PC/104p BiSerial is PC/104p compliant per the PC/104p specification. | |

| |

|

| The PC/104p BiSerial is PCI compliant. You can develop with a PCI to PC/104p adapter - PCI2PC/104p |