PMC-Serial

Highly flexible Communications Interface

with Synchronous and Asynchronous Serial Protocols

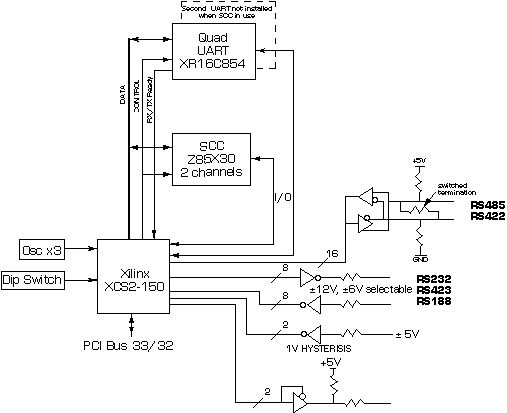

UART and SCC

| Single wide PMC. |

|

| |

|

| Quad UART - XR854 with 128 byte FIFO's. Locations for 2 devices [8 UARTs], full modem controls on some channels |

|

| |

|

| Zilog 85x30 enhanced Serial Communications Controller . |

|

| RS232, RS485, RS423, RS188, tristate buffers available. VHDL programming options and build options provide multiple combinations. Up to 24 differential and up to 48 single ended IO plus AUX In and Out. |

|

| |

|

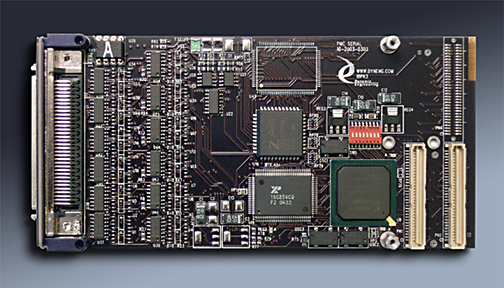

| Industry standard SCSI III front panel IO and Pn4 backplane connection. IO is selectable as a build option. Pn4 IO is compatible with the PIM-Parallel IO |

|

| |

|

| All FPGA registers are read-writeable. UART and SCC registers defined by those devices |

|

| |

|

| UART and SCC can be programmed independently to cause interrupts. Interrupts are mapped to INTA on PCI bus. Polled and interrupt driven capability. |

|

| |

|

| +5V, +12, -12. |

|

| |

|

| All IO Channels are protected with limiting resistors. |

|

| |

|

| |

|

| Separate Oscillators for UART and SCC. |

|

| |

|

| Custom state machine can be supported with PCI derived or external oscillator based frequencies. |

|

| 8 position switch provided for positive identification in PCI systems with multiple PMC-Serial cards. Other user defined purposes. Readable via register. |

|

| With the integrated PCI to UART and PCI to SCC Bridge featured in the PMC-Serial standard accesses to your hardware happens faster than in competing designs. Throughput is further enhanced when the UART pre-read and data packing modes are used. |

|

| |

|

| PMC-Serial can potentially replace 2 or more alternate PMC´s with the combination of UART(s), SCC, custom state-machines and buildable IO features. Save cards, Save slots, Save $. |

|

| |

|

| PMC-Serial is easy to use. A point and shoot user interface to the UART´s and SCC. Please download the manual and see for yourself. The engineering kit provides a good starting point for a new user. |

|

| |

|

| PMC-Serial is a popular board. We keep the PMC-Serial in stock. Send in your order and we will get it to you promptly. Custom versions can be dialed in quickly as well as customer requested VHDL features. |

|

| |

|

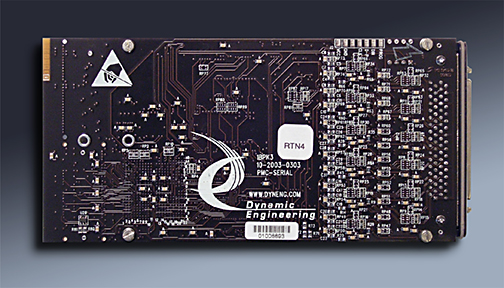

| PMC-Serial is a standard single wide PMC [single slot] board which conforms to the PMC mechanical and electrical specifications. Eliminate mechanical interference issues. |

|

| |

|

| PMC-Serial is PMC compliant per the IEEE 1386 specification. | |

| |

|

| PMC-Serial is PCI compliant. You can develop with a PCI /PCIe to PMC adapter - PCI2PMC or PCIeBPMCX1. |