IP-Parallel-IO

Seven Standard Models with combinations of upto 48 TTL and 24 differential

Order This Item

When LVDS is selected, the differential devices for the ordered part number will be replaced with LVDS devices. Default is RS-485 as shown in the base PNs.IP-Parallel-IO Description

- 7 combinations of TTL and 485/LVDS IO available

- Each IO is independent

- Plug and Play operation

- Windows and Linux Drivers available

- 1 year warranty standard. Extended warranty available.

- ROHS and Standard processing available

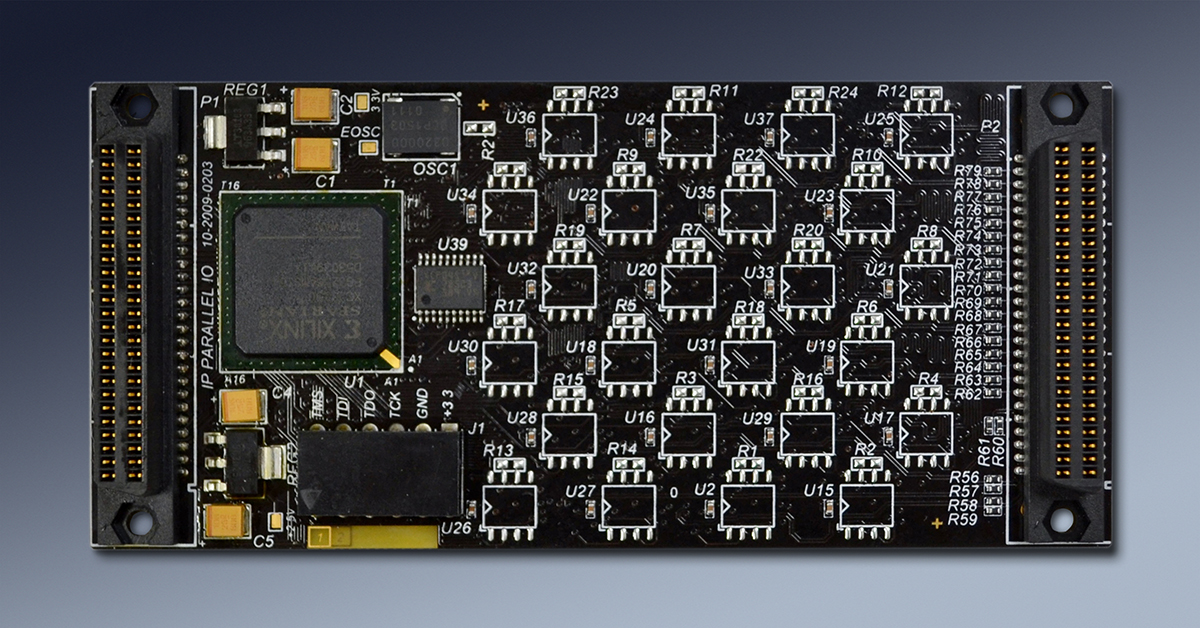

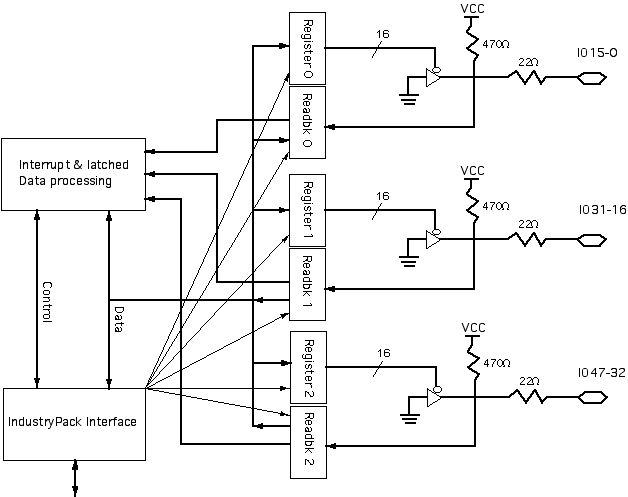

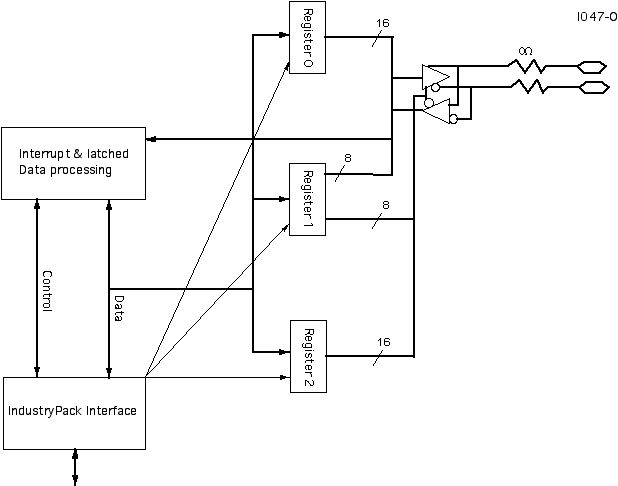

IP-Parallel-IO Block Diagram

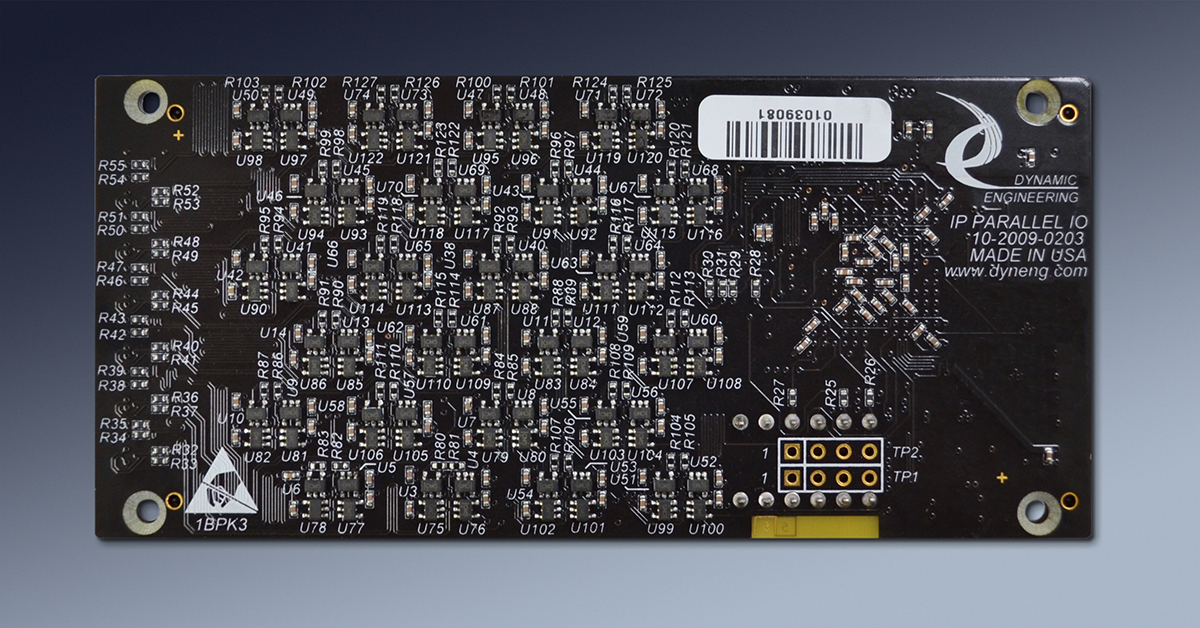

The IndustryPack® compatible IP-Parallel-IO with counter and timer design provides 48 digital parallel IO lines in one IP module slot of your carrier board. These IO´s can be configured to be TTL or RS485 compatible in several combinations. A real space saver for systems with both types of IO. Perfect for your embedded control applications. Please download the manual [see bottom of page] for more information. IP-Parallel is available as an add-on IndustryPack Module for use with carriers on all of the common buses: VPX, VME, cPCI, PCI, PCIe, and PC104p. IP-Parallel is supported for both Windows® and Linux.

The IP Module driver can be instantiated multiple times to control multiple cards by the same CPU. IP-Parallel-IO when coupled with the Dynamic Driver "knows" what slot it is in and which carrier it is installed into. The slot and carrier information is required when using multiple cards in a PCI system with dynamic address assignment. A known system configuration can be combined with the slot and carrier information to deterministically access the right card. The IP Driver can determine which type of IP-Parallel is installed and load the correct driver. All 7 types of the base design are supplied with the IP Parallel Windows® driver.

PCIe implementations are supported with the PCIe3IP and PCIe5IP.

Applications from 1 to 240 TTL lines and/or 1 - 120 Differential pairs per PCIe slot.

PCI implementations are supported with the PCI3IP and PCI5IP.

Applications from 1 to 240 TTL lines and/or 1 - 120 Differential pairs per PCI slot.

cPCI 3U is supported with the cPCI2IP. Applications from 1 to 96 TTL lines and/or 1 - 48 Differential pairs.

cPCI 6U is supported with the cPCI4IP. Applications from 1 to 192 TTL lines and/or 1 - 96 Differential pairs.

PC104p is supported with the PC104pIP. Applications from 1 to 48 TTL lines and/or 1 - 24 Differential pairs.

PC104p situations with a custom mechanical can be done with the PC104p4IP.

Channel counts from 1 to 192 TTL lines and/or 1 - 96 Differential pairs per PC104 stack position.

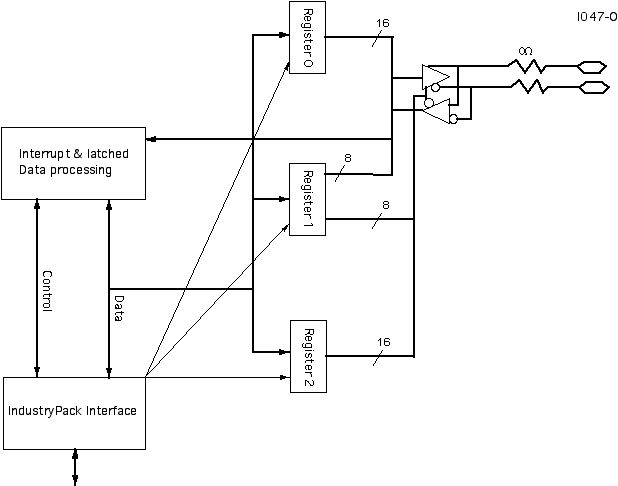

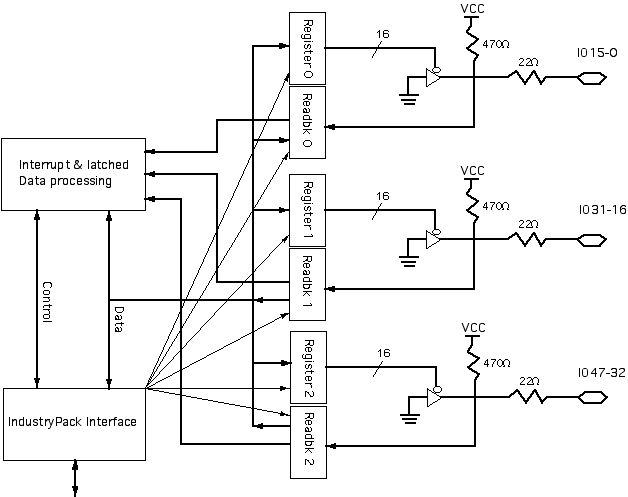

IP-Parallel-485 Block Diagram

Each channel is programmable to be an input, or an output on a channel-by-channel basis via software. All DIO channels can be used as interrupt generators. Interrupts are programmable to be enabled, active high or low, and edge or level triggered. The registers are mapped as 16 bit words. All control registers are read-writeable.

Outputs in TTL mode are driven with 24 mA open-drain devices to allow multi-drop applications. 470 ohm pull-up resistors are provided. In 485 mode individual transceivers provide direction control and RS485 compatibility.

An external oscillator position is provided for custom applications.

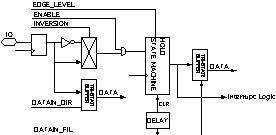

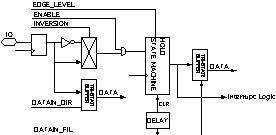

IP-Parallel-IO IO Filter and Interrupt Control Block Diagram

Frequently it is necessary to correlate the time and the event. The IP-Parallel design supports an enhanced MC68230 capability with two - 32 bit counter - timers. The counter-timers are easy to use with a minimum of registers to access and complete independence. The IP clock is used as a reference; both 8 and 32 MHz can be used.

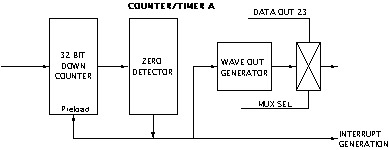

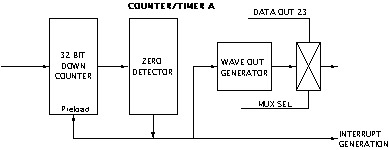

Counter/Timer A features a 32 bit down-counter with a pre-load register. The counter output is tested against a "zero" value. When zero the counter is re-loaded with the pre-load value to create a cycle. At each zero detection an interrupt can be generated. At each zero detection a waveform can be transitioned. The waveform can be enabled onto the upper data bit.

IP-Parallel-IO Counter - Timer A Block Diagram

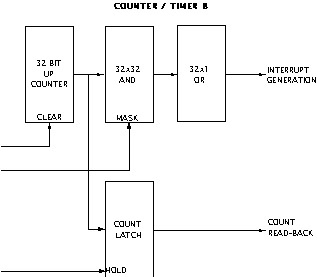

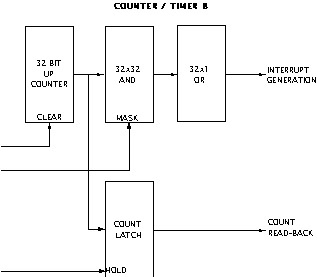

Counter / Timer B has a 32 bit up counter which can be cleared by the software. The counter output is masked with a user programmable value to select a particular counter bit or bits to use for interrupt creation. The counter output is also available to read via software and can serve as a real-time clock.

IP-Parallel-IO Counter - Timer B Block Diagram

The IndustryPack® compatible IP-Parallel-IO with counter and timer design provides 48 digital parallel IO lines in one IP module slot of your carrier board. These IO´s can be configured to be TTL or RS485 compatible in several combinations. A real space saver for systems with both types of IO. Perfect for your embedded control applications. Please download the manual [see bottom of page] for more information. IP-Parallel is available as an add-on IndustryPack Module for use with carriers on all of the common buses: VPX, VME, cPCI, PCI, PCIe, and PC104p. IP-Parallel is supported for both Windows® and Linux.

The IP Module driver can be instantiated multiple times to control multiple cards by the same CPU. IP-Parallel-IO when coupled with the Dynamic Driver "knows" what slot it is in and which carrier it is installed into. The slot and carrier information is required when using multiple cards in a PCI system with dynamic address assignment. A known system configuration can be combined with the slot and carrier information to deterministically access the right card. The IP Driver can determine which type of IP-Parallel is installed and load the correct driver. All 7 types of the base design are supplied with the IP Parallel Windows® driver.

PCIe implementations are supported with the PCIe3IP and PCIe5IP.

Applications from 1 to 240 TTL lines and/or 1 - 120 Differential pairs per PCIe slot.

PCI implementations are supported with the PCI3IP and PCI5IP.

Applications from 1 to 240 TTL lines and/or 1 - 120 Differential pairs per PCI slot.

cPCI 3U is supported with the cPCI2IP. Applications from 1 to 96 TTL lines and/or 1 - 48 Differential pairs.

cPCI 6U is supported with the cPCI4IP. Applications from 1 to 192 TTL lines and/or 1 - 96 Differential pairs.

PC104p is supported with the PC104pIP. Applications from 1 to 48 TTL lines and/or 1 - 24 Differential pairs.

PC104p situations with a custom mechanical can be done with the PC104p4IP.

Channel counts from 1 to 192 TTL lines and/or 1 - 96 Differential pairs per PC104 stack position.

IP-Parallel-485 Block Diagram

Each channel is programmable to be an input, or an output on a channel-by-channel basis via software. All DIO channels can be used as interrupt generators. Interrupts are programmable to be enabled, active high or low, and edge or level triggered. The registers are mapped as 16 bit words. All control registers are read-writeable.

Outputs in TTL mode are driven with 24 mA open-drain devices to allow multi-drop applications. 470 ohm pull-up resistors are provided. In 485 mode individual transceivers provide direction control and RS485 compatibility.

An external oscillator position is provided for custom applications.

IP-Parallel-IO IO Filter and Interrupt Control Block Diagram

Frequently it is necessary to correlate the time and the event. The IP-Parallel design supports an enhanced MC68230 capability with two - 32 bit counter - timers. The counter-timers are easy to use with a minimum of registers to access and complete independence. The IP clock is used as a reference; both 8 and 32 MHz can be used.

Counter/Timer A features a 32 bit down-counter with a pre-load register. The counter output is tested against a "zero" value. When zero the counter is re-loaded with the pre-load value to create a cycle. At each zero detection an interrupt can be generated. At each zero detection a waveform can be transitioned. The waveform can be enabled onto the upper data bit.

IP-Parallel-IO Counter - Timer A Block Diagram

Counter / Timer B has a 32 bit up counter which can be cleared by the software. The counter output is masked with a user programmable value to select a particular counter bit or bits to use for interrupt creation. The counter output is also available to read via software and can serve as a real-time clock.

IP-Parallel-IO Counter - Timer B Block Diagram

IP-Parallel-IO Features

Size

1.8x3.9 inches nominal single slot IP Module. Type II with low profile devices on rear

IO

IP Module IO connector

Clocks

Compatible with 8 and 32 MHz IP bus operation. Oscillator position available

IP Decoding

ID, IO, Mem and INT spaces supported.

Parallel Interface

Up to 48 independent TTL, and up to 24 Differential channels per module. Carrier determines number of modules that can be installed. Each channel can be an input or an output. Read-back filtered or direct.

IO Configuration

IO can be configured as single ended with open drain 24mA drivers and 470 ohm pull-ups or dfferential pairs.

Interface

Open drain drivers or 485 transceivers

Synchronization

Outputs can be synchronized to change together [across register boundaries]. Synchronization can be disabled.

Pull-up Resistor

470 standard, 1K, 4.7K available on TTL lines.

Counter / Timer

Two independent Counter / Timer functions are provided.

CTA: 32 bit down-counter with registered initial value and auto-preload. Waveform generator. Interrupt generator based on zero detection.

CTB: 32 bit up-counter with clear and read-back. Bitwise selectable interrupt generator.

CTA: 32 bit down-counter with registered initial value and auto-preload. Waveform generator. Interrupt generator based on zero detection.

CTB: 32 bit up-counter with clear and read-back. Bitwise selectable interrupt generator.

Interrupts

All IO Channels can be programmed to cause interrupts. Each channel is programmable to be masked, active hi, active low, edge or level sensitive. Master enable for data channels. Separate enable for each data channel, CTA, and CTB. Status register with current interrupt request status. Interrupts are mapped to INTR0n on IP bus. Master enable can be disabled to allow polled operation.

Power Requirement

+5V. Approximately 52 mA at 5V typical unloaded.

SW Interface

All FPGA registers are read-write. All registers on word addresses.

Current Fab Number

10-2001-0103

Reliability

1.496 million hours GB 25C Bellcore MTBF

Custom

There is room in the FPGA for custom applications. Send in your specifications and we can quote a custom version for you

IP-Parallel-IO Benefits

Speed

The IP interface supports 32 MHz operation for quick data loading and unloading. The interface supports interrupts and polling. Dynamic Engineering carriers support 64 bit[PCIe models]/32 bit[PCI models] to 16 bit conversion in HW allowing for higher throughput and lower overhead.

Price

System level cost is best when reasonably priced reliable hardware is used and NRE minimized. With IP-Parallel-IO, driver support for the carrier and IP level, reference software, history of reliable operation, and fantastic client support your cost per unit and overall costs are attractive. IP-Parallel-IO is inexpensive and can save money in other ways too. IP Parallel IO can take the place of three other IP´s with it´s combination of TTL, 485, and counter timer functions.

Ease of Use

IP-Parallel-IO is easy to use. A point and shoot user interface. Please download the manuals and see for yourself. The engineering kit provides a good starting point for a new user. The User Application software and driver will get you up and running quickly. SIngle and multiple card capable. The driver has direct calls to read or set any of the IO lines. The example software includes loop-back testing. Interrupts are supported with the driver, and tested with the reference software.

Availability

The IP-Parallel-IO family are stocked items.

IP Specification Compatibility

IP-Parallel-IO is compliant per the VITA 4 - 1995 specification. Tested with PCI and PCIe based carriers. All Dynamic Engineering IP Modules are compatible with the PCIe3IP, PCIe5IP, VPXI2IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP etc. IP-Parallel-IO will operate with any IP specification compliant carrier board.

Part Number: IP-Parallel-IO

Ordering Options

-

Replace the "IO" with the following options:

- -TTL 48 TTL IO

- -1 40 TTL & 4 RS-485 transceivers

- -2 32 TTL & 8 RS-485 transceivers

- -3 24 TTL & 12 RS-485 transceivers

- -4 16 TTL &16 RS-485 transceivers

- -5 8 TTL & 20 RS-485 transceivers

- -485 24 RS-485 transceivers

- -XXX See Manuals section for customized versions and replace XXX with type

- -ROHS Use ROHS processing. Standard processing is "leaded"

- -CC Option to add Conformal Coating

- -LVDS Switch to LVDS IO for any Differential IO installed

- -TERM Add parallel 100 ohm terminations to any Differential IO installed

Add additional options to the "- number"

IP-Parallel-IO Drivers

Software Support for IP-Parallel-IO includes: Windows® and Linux compliant drivers

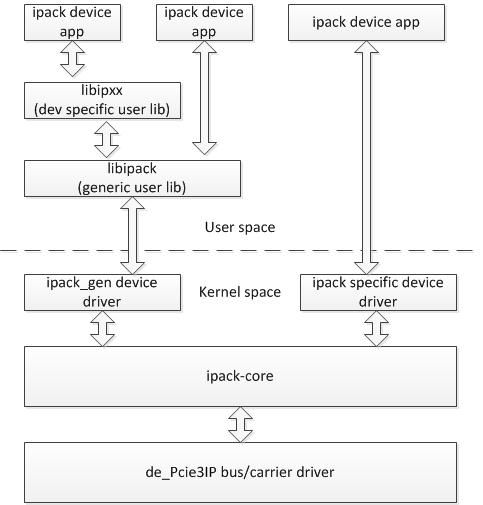

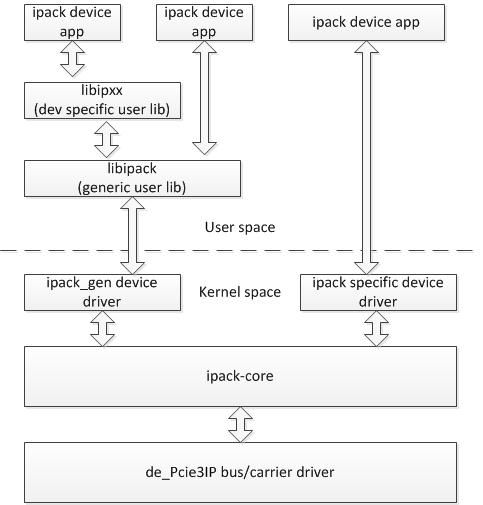

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of IP-Parallel-IO implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of IP-Parallel-IO implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

IP-Parallel-IO Manuals

Click on the links to Download selected manuals in PDF format.

IP Carrier and Module Quick Start guide for Windows®7

IP Carrier and Module Quick Start guide for Windows®10

IP-Parallel-IO HW Manual covers -485, -TTL, -1, -2, -3, -4, and -5 models

IP-Parallel-IO Driver Manual for Windows® 10 - new unified driver package

VxWorks IP Module Manual

IP Carrier Linux Manual

Linux IP Module Manual

Please Download the IP-Parallel-IO Manual Previous Standard Product HW Manual covers -485, -TTL, -1, -2, -3, -4, and -5 models

IP-Parallel-IO Driver Manual for Windows® 7

Customer Special Versions

You can order these too or request that we design one for you

IP Parallel IO version BA1 "Tape"

Customer: Boeing : Interface with a cartridge tape device. Memory access to IP triggers data transfer with cartridge. 22 Address, 16 Data, 1 Parity, 4 control bits, 5 Status read and write cycles supported. Win7 SW package. Click through for additional information, manuals, timing diagrams.

Customer: Lockheed Martin: IndustryPack® based interface to LARS CDU [Lightweight Airborne Recovery System Control Display Unit]

When the IP-Parallel-CDU is powered-on it defaults to a dedicated serial interface that uses four IO lines to implement a full-duplex NRZ serial clock and data protocol. The transmit interface defaults to 32-bit LSB first at 500 kHz bit rate. Both the clock rate and the number of bits are programmable. The receive interface uses an external clock at a nominal rate of 614 kHz, and will function over a wide range of frequencies. The receive words default to 32-bits LSB first. The word size is programmable.

Download the IP-Parallel-CDU Manual

IndustryPack® based interface to Dual Port RAM

IP-Parallel-TTL-DPR provides a parallel interface to interconnect with a memory based system. A19-0, D15-0, READ, WRITE, ACK, BUSY supported. 100 MHz reference used to have precise timing. Simple structure to send commands to the interface to Write to memory, Read from memory and Read multiple from memory. Commands stored in 255 deep FIFO queue. 1Kx16 FIFO to store data from Read commands. In addition, an 8 bit GPIO parallel port with COS [change of state] capability is provided. Programmable sample rate for COS operation. Win10/11 support. Target simulator developed for test purposes. If your timing is different let us know know and we can modify to suit your requirements.

Download the IP-Parallel-TTL-DPR Manual

Download the IP-Parallel-TTL-DPR Win10 Win11 Manual

IP Carrier and Module Quick Start guide for Windows®7

IP Carrier and Module Quick Start guide for Windows®10

IP-Parallel-IO HW Manual covers -485, -TTL, -1, -2, -3, -4, and -5 models

IP-Parallel-IO Driver Manual for Windows® 10 - new unified driver package

VxWorks IP Module Manual

IP Carrier Linux Manual

Linux IP Module Manual

Please Download the IP-Parallel-IO Manual Previous Standard Product HW Manual covers -485, -TTL, -1, -2, -3, -4, and -5 models

IP-Parallel-IO Driver Manual for Windows® 7

Customer Special Versions

You can order these too or request that we design one for you

IP Parallel IO version BA1 "Tape"

Customer: Boeing : Interface with a cartridge tape device. Memory access to IP triggers data transfer with cartridge. 22 Address, 16 Data, 1 Parity, 4 control bits, 5 Status read and write cycles supported. Win7 SW package. Click through for additional information, manuals, timing diagrams.

Customer: Lockheed Martin: IndustryPack® based interface to LARS CDU [Lightweight Airborne Recovery System Control Display Unit]

When the IP-Parallel-CDU is powered-on it defaults to a dedicated serial interface that uses four IO lines to implement a full-duplex NRZ serial clock and data protocol. The transmit interface defaults to 32-bit LSB first at 500 kHz bit rate. Both the clock rate and the number of bits are programmable. The receive interface uses an external clock at a nominal rate of 614 kHz, and will function over a wide range of frequencies. The receive words default to 32-bits LSB first. The word size is programmable.

Download the IP-Parallel-CDU Manual

IndustryPack® based interface to Dual Port RAM

IP-Parallel-TTL-DPR provides a parallel interface to interconnect with a memory based system. A19-0, D15-0, READ, WRITE, ACK, BUSY supported. 100 MHz reference used to have precise timing. Simple structure to send commands to the interface to Write to memory, Read from memory and Read multiple from memory. Commands stored in 255 deep FIFO queue. 1Kx16 FIFO to store data from Read commands. In addition, an 8 bit GPIO parallel port with COS [change of state] capability is provided. Programmable sample rate for COS operation. Win10/11 support. Target simulator developed for test purposes. If your timing is different let us know know and we can modify to suit your requirements.

Download the IP-Parallel-TTL-DPR Manual

Download the IP-Parallel-TTL-DPR Win10 Win11 Manual