cPCI-DartBase

cPCI 3U Compatible Base Board to support mezzanine cards

cPCI-DartBase Description

- cPCI 3U

- 3.3V/32/33 PCI interface with DMA support

- Local power supplies to support Xilinx and other FPGAs on Mezzanine Card

- Analog and Digital supplies

- 8 bi-directional LVDS communication pairs between DartBase and installed Mezzanine

- Separate LVDS control loop for set-up.

- PXI triggering routed from J2 to Mezzanine connector

- JTAG and reprogramable Xilinx FPGA support for Mezzanine card

- Optional "Zero Slot Fans"™

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature standard.

- ROHS and Standard processing available

cPCi-DartBase was designed in 2008. This webpage is provided for reference purposes. If you like the concept and want to purchase we can update the design to be manufacturable with current parts etc. We can also enhance the design to make use of the newer FPGAs. In addition, PCIe-AlteraCycloneIV is available with PCIe-Spartan-VI due for release. The Spartan VI derivative is planned to be ported to cPCI to provide a user programmable solution for this platform. Please contact Dynamic Engineering for more information on either of the Spartan Vi products.

Do you need to develop your own cPCI application HW and prefer a mezzanine approach? Dynamic Engineering offers a line of PMC carriers and the cPCI-DartBase for this purpose. The advantages of "DartBase" include access to more of the cPCI 3U bezel, more built in power options, more surface area for the mezzanine and fewer pins required for the bus interface. Analog, Digital and mixed designs are supported with the clean power supplies and tied at the connector analog and digital return paths. For PXI chassis the clocks and timing control signals are routed to the mezzanine position.

Power from the cPCI system is routed to the mezzanine connector to support the +/-12V, 3.3 and 5V rails. In addition the 5V is used with buck and boost supplies to create +/- 6V power rails. The 6V rails are provided to the mezzanine and used to generate the 1.25V and 2.5V ref voltages through linear supplies to serve as analog references. 1.5A of 2.5V analog power is also supplied with a linear regulator from the 3.3V supply for operating analog circuits. Approximately 2A each of 1.2V and 2.5V power is supplied to operate an FPGA´s core voltages. The analog and digital grounds are tied together via 6A ferrite bead. The analog voltages can be used for digital purposes if desired.

When installed in a PXI chassis the system clock and triggers may be available. PXI_TRIG0 - PXI_TRIG7, PXI_CLK10, and PXI_STAR are routed from J2 to the mezzanine control connector.

JTAG programming can be used to update FLASH on the mezzanine card. A header mounted to the DartBase is routed to the mezzanine connector. In addition the control and programming lines are tied between a port on the local FPGA and programming port on the mezzanine FPGA to allow reprogramming on-the-fly. The DartBase design has the logic and the Driver supports reprogramming the mezzanine FPGA for reprogrammability. A handy feature for development and field based updates. Please note: the target FPGA is a Spartan family part. DartBase may need to be updated to support an Altera based design in this manner.

In PCI based systems the address of the installed cards is unknown until run time. With multiple cards of the same type in a system SW designers run the risk of controlling the wrong assets or making decisions based on the wrong input. The DartBase design includes a simple remedy. An octal switch is provided for positive identification of an individual card in a multi-card environment. The driver for the card can read the switch and allow the application software to make a positive association between a specific card and its "handle".

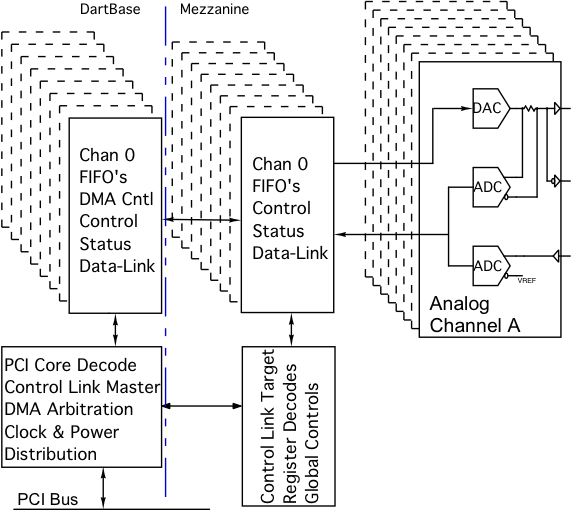

Many times you need more than one port of the same type, or several different ports on the same card. There are 8 channels designed into the DartBase structure to allow for up to 8 devices [same or different] to be directly controlled and with individual DMA capability. The DartBase design includes the DMA arbitration and memory elements to support DMA access or standard R/W access on each channel. In addition there is a control link which can be used to do top level set-up and control. As an example you can put 8 ports on the mezzanine each with DMA transmit and DMA receive support. Each port can operate independently with the DartBase architecture. The first mezzanine developed has 8 channels of Analog circuitry to stimulate and read-back data for a biometrics application.

The DartBase design is intended to be flexible allowing for a variety of connectors at the bezel, types of IO implemented etc. The Bezel for DartBase is designed to accomodate wider connectors than on PMC and other standard mezzanine cards.

"Zero Slot fans"™ can be installed to provide direct cooling to the main component side of the installed mezzanine. The fans provide approximately 5 CFM each.

The single width PMC specification is for 149x74 mm [5.866" x 2.91"] with area lost for 4 PMC connectors and 2 voltage keying holes. The DartBase design uses LVDS ports to communicate between the mezzanine and the Base allowing 8 channels plus the control channel to reside in one connector. Power is through a second connector. Since LVDS levels are defined there is no need for voltage keying holes. The area of the Dart Mezzanine has been expanded to be 6.293" x 3.7". The added area coupled with the reduced connectors and holes provides for more usable space. In addition the connector mounting positions are set to allow the FPGA to be mounted below the connectors and the IO above. This configuration allows for better performance with mixed analog and digital circuitry.

To make integration easy an engineering kit is available. The engineering kit includes an Altium compatible project to help ensure your mezzanine fits properly. If you choose to use one of our standard mezzanines you can get the VHDL for it to allow you to make changes for your project. A windows® driver is also part of the engineering kit. Linux is available upon request. The driver makes accomodations for user defined registers - for when you do your own project and do not want to write your own driver.

Frequently clients ask Dynamic Engineering to do the initial programming for their project and then deliver a custom engineering kit with the initial implementation of the mezzanine, custom driver and manuals to them. In this state the client can do the maintenance or add features while taking advantage of Dynamic Engineering´s expertise and familiarity with cPCI-DartBase. Dartmouth worked with Dynamic Engineering to develop the "DartBoard" depicted in the combined block diagram.

Do you need to develop your own cPCI application HW and prefer a mezzanine approach? Dynamic Engineering offers a line of PMC carriers and the cPCI-DartBase for this purpose. The advantages of "DartBase" include access to more of the cPCI 3U bezel, more built in power options, more surface area for the mezzanine and fewer pins required for the bus interface. Analog, Digital and mixed designs are supported with the clean power supplies and tied at the connector analog and digital return paths. For PXI chassis the clocks and timing control signals are routed to the mezzanine position.

Power from the cPCI system is routed to the mezzanine connector to support the +/-12V, 3.3 and 5V rails. In addition the 5V is used with buck and boost supplies to create +/- 6V power rails. The 6V rails are provided to the mezzanine and used to generate the 1.25V and 2.5V ref voltages through linear supplies to serve as analog references. 1.5A of 2.5V analog power is also supplied with a linear regulator from the 3.3V supply for operating analog circuits. Approximately 2A each of 1.2V and 2.5V power is supplied to operate an FPGA´s core voltages. The analog and digital grounds are tied together via 6A ferrite bead. The analog voltages can be used for digital purposes if desired.

When installed in a PXI chassis the system clock and triggers may be available. PXI_TRIG0 - PXI_TRIG7, PXI_CLK10, and PXI_STAR are routed from J2 to the mezzanine control connector.

JTAG programming can be used to update FLASH on the mezzanine card. A header mounted to the DartBase is routed to the mezzanine connector. In addition the control and programming lines are tied between a port on the local FPGA and programming port on the mezzanine FPGA to allow reprogramming on-the-fly. The DartBase design has the logic and the Driver supports reprogramming the mezzanine FPGA for reprogrammability. A handy feature for development and field based updates. Please note: the target FPGA is a Spartan family part. DartBase may need to be updated to support an Altera based design in this manner.

In PCI based systems the address of the installed cards is unknown until run time. With multiple cards of the same type in a system SW designers run the risk of controlling the wrong assets or making decisions based on the wrong input. The DartBase design includes a simple remedy. An octal switch is provided for positive identification of an individual card in a multi-card environment. The driver for the card can read the switch and allow the application software to make a positive association between a specific card and its "handle".

Many times you need more than one port of the same type, or several different ports on the same card. There are 8 channels designed into the DartBase structure to allow for up to 8 devices [same or different] to be directly controlled and with individual DMA capability. The DartBase design includes the DMA arbitration and memory elements to support DMA access or standard R/W access on each channel. In addition there is a control link which can be used to do top level set-up and control. As an example you can put 8 ports on the mezzanine each with DMA transmit and DMA receive support. Each port can operate independently with the DartBase architecture. The first mezzanine developed has 8 channels of Analog circuitry to stimulate and read-back data for a biometrics application.

The DartBase design is intended to be flexible allowing for a variety of connectors at the bezel, types of IO implemented etc. The Bezel for DartBase is designed to accomodate wider connectors than on PMC and other standard mezzanine cards.

"Zero Slot fans"™ can be installed to provide direct cooling to the main component side of the installed mezzanine. The fans provide approximately 5 CFM each.

The single width PMC specification is for 149x74 mm [5.866" x 2.91"] with area lost for 4 PMC connectors and 2 voltage keying holes. The DartBase design uses LVDS ports to communicate between the mezzanine and the Base allowing 8 channels plus the control channel to reside in one connector. Power is through a second connector. Since LVDS levels are defined there is no need for voltage keying holes. The area of the Dart Mezzanine has been expanded to be 6.293" x 3.7". The added area coupled with the reduced connectors and holes provides for more usable space. In addition the connector mounting positions are set to allow the FPGA to be mounted below the connectors and the IO above. This configuration allows for better performance with mixed analog and digital circuitry.

To make integration easy an engineering kit is available. The engineering kit includes an Altium compatible project to help ensure your mezzanine fits properly. If you choose to use one of our standard mezzanines you can get the VHDL for it to allow you to make changes for your project. A windows® driver is also part of the engineering kit. Linux is available upon request. The driver makes accomodations for user defined registers - for when you do your own project and do not want to write your own driver.

Frequently clients ask Dynamic Engineering to do the initial programming for their project and then deliver a custom engineering kit with the initial implementation of the mezzanine, custom driver and manuals to them. In this state the client can do the maintenance or add features while taking advantage of Dynamic Engineering´s expertise and familiarity with cPCI-DartBase. Dartmouth worked with Dynamic Engineering to develop the "DartBoard" depicted in the combined block diagram.

PCI3IP Features

Size

Standard 3U cPCI

System Interface

Standard 32/33 3V PCI interface supported. Channelized DMA supported on 8 bidirectional channels.

Mezzanine Interface

8 high-speed full duplex serial links to support 8 channels plus back door control bus for setting up mezzanine registers eetc. 2.5V differential levels based on Xilinx FPGA. Recommend Spartain III or higher performance device fro mezzanine interface.

Memory

4Kx32 FIFO per channel direction to support DMA [16 total].

PXI

The PXI timing signals are routed from J2 to the mezzanine position. It is optional to the mezzanine whether the PXI timing signals are used.

Power Supplies

Multiple voltages are supported: 1.2V, 2.5V, 3.3V, 5V, 6V, -6V, 12V, -12V are supplied to the mezzanine position. With a Xilinx FPGA implemented on the mezzanine, the standard core and IO voltages are available without needing a local power supply. Several of the voltages have analog and digital versions available at the mezzanine power connector.

Fan

2 "Zero Slot Fans"™ can be installed to provide direct cooling to the main component side of the installed mezzanine.

JTAG

A header is provided with the standard JTAG signals routed to the mezzanine IO connector. This connector can be used to reprogram FLASH etc. located on the mezzanine card. In addition, the FPGA on the mezzanine [Xilinx] can be reprogramed via DartBase card. This is handy for development or field upgrades.

Bezel

cPCI-DartBase is outfitted with a 3U bezel. The bezel has a large cutout to allow for connectors mounted to the installed Mezzanine.

Software Interface

Windows® drivers are available with DMA support, register control, and mezzanine IO control. Linux available upon request. DartBoard mezzanine support included plus user defined spaces for each channel.

DIP Switch

An 8 position switch is attached to the base FPGA to allow for configuration control, addressing multiple cards, or to facilitate debugging.

Classified/Proprietary Designs

Since the mezzanine contains all of the personality for your sensitive design, Dynamic Engineering can help by providing a starting point or completed design based on a sanitized requirement and you can put on the finishing touches or provided maintenance upgrades in the future.

cPCI-DartBase Benefits

Speed

cPCI-DartBase is optimized for IO interfacing requirements. The FIFO memories and programmable interrupts off-load the CPU from most of the management. Independent DMA channels further reduce CPU overhead when multiple streams are in use. FIFO access is optimized for the PCI bus further reducing overhead by speeding up the data transfer. IO is provided by the mezzanine allowing for all possibilities.

Price

cPCI-DartBase is available off-the-shelf at a reasonable price. Custom versions can also be arranged. cPCI-DartBase supports the mezzanine with power, control and data path support, DMA and local channel arbitration, allowing the mezzanine to be optimized for your requirements. Since the PCI bus is handled and drivers are available, your integration costs will be lower. Previously implemented custom designs are available wihtout the costs of schematic level design, layout, debugging etc. When a new Mezzanine is required for your application, Dynamic Engineering can draw upon the many years of experience to create a custom implementation that meets budgetary constraints.

Ease of Use

cPCI-DartBase is easy to use. DartBase is essentially auto-configuring with very little set-up required. With the PCI interface along the channelized DMA incorporated into the DartBase, the user interface on the mezzanine is much less complex. Dynamic Engineering can provide a complete solution including the mezzanine or support to allow you to develop your own. PADs layout files, reference VHDL, reference schematics etc. are available to support your design effort.

Availability

We work to keep cPCI-DartBase in stock. Dynamic Engineering has in house manufacturing capabilities for short lead times on larger orders.

Size

cPCI-DartBase is standard single width 3U cPCI card and meets the cPCI mechanical specifications.

cPCI Compatibility

cPCI-DartBase is a cPCI compliant per the cPCI specification

PCI Compatibility

cPCI-DartBase is a PCI compliant per the PCI specification

Part Number: cPCI-DartBase

Ordering Options

- cPCI-DartBase Standard board cPCI 3U compatible base board to support mezzanine cards Add any of the following build options after the PN as shown below:

- -ROHS Use ROHS processing. Standard processing is "leaded"

- -CC Option to add Conformal Coating

cPCI-DartBase Drivers

Software Support for cPCI-DartBase includes: Windows® and Linux compliant drivers

Please see the Driver manuals for the specifics of each type.

Please see the Driver manuals for the specifics of each type.

cPCI-DartBase Manuals

cPCI-DartBase Hardware Manual Hardware level design description, bit maps, pinouts, operation etc. Includes definitions for Dynamic Engineering designed Mezzanines.

cPCI-DartBase Software Manual User Driver manual for installation and use with API for Dynamic Engineering designed Mezzanines.

cPCI-DartBase Software Manual User Driver manual for installation and use with API for Dynamic Engineering designed Mezzanines.