VPX-GLIB

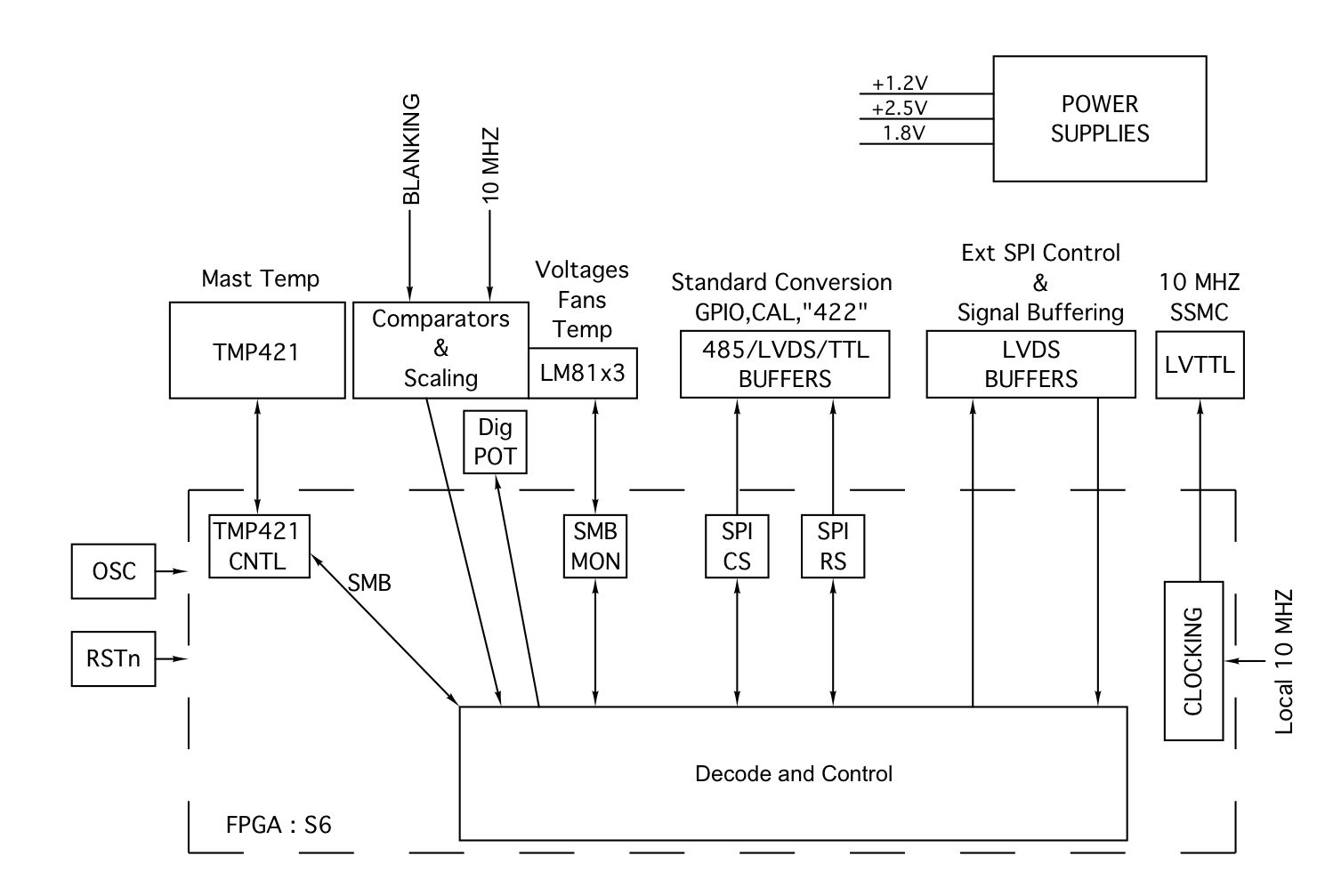

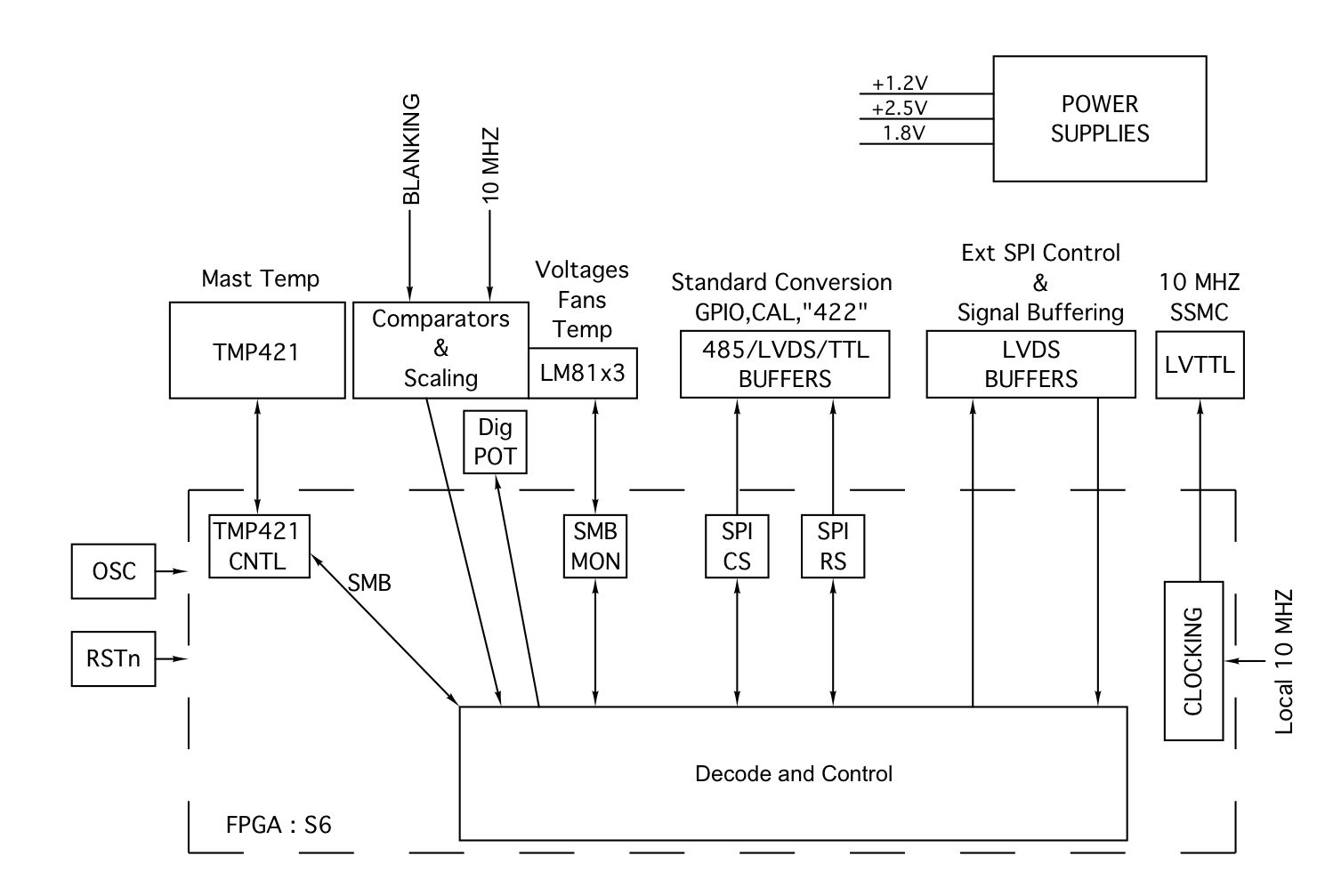

VPX Module with Spartan 6 FPGA, Interfaces to SPI, SMB, temperature, voltage, fan speed sensors, plus LVDS, 485, TTL conversion, 10 MHz reference clock support

Order This Item

VPX-GLIB Description

- VPX 3U module with option for wedgelocks

- Spartan 6 FPGA with BRAM for FIFO or RAM implementation

- PCIe and SPI interfaces

- 485 and LVDS differential IO. Most with programmable termination and direction.

- Electrical conversion between IO types

- Rear IO, other than 10 MHz reference from bezel mounted coax [ssmc]

- SMB conversion from SPI to control 3 LM81s FAN speed x4, Voltage measurements [3x +15, 4x +12V, 8V, 5V, -8V, 2x -15V, plus internal voltages]

- Remote Temperature measurement input

- GPIO [TTL and LVDS]

- Blanking inputs with SW programmable offset

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature standard.

- ROHS and Standard processing available

VPX-GLIB [Global Interface Board] is a multi-purpose hardware design supplying many system supervisor and space saving interfaces. VPX-GLIB is controlled via SPI bus [LVDS] using CLK, EN, SEL [2-0], MOSI, MISO. Currently the SEL encoding 000, and 001 are used for internal SPI controlled register access with SEL 010 used for conversion to SMB. The SPI interface with the CPU is received and decoded. SPI accesses to internal functions are re-routed to a second decoder which extracts data to be written or packages data to be read. The extracted data is stored into a local register, and then parallel loaded to the target register. The size of the data is programmable within the VHDL. Messages of incorrect length are filtered - keeping the initial message and dumping the extra clocks. Each of the local registers has a separate data path [parallel] back to the encoder/decoder. The address received selects the mux output desired and the state-machine returns the requested data.

The FPGA is a Spartan VI LX25. The FPGA can be reprogrammed via JTAG to add new features. We mount to PCIe8LSwVPX3U for test and programming purposes. Most of the differential IO is programmable for direction and termination allowing for direction changes etc.

The FPGA receives 50 MHz from the oscillator. The clock input is doubled to 100 MHz and used locally for decoding SPI signaling and operating miscellaneous state-machines.

A TCXO oscillator provides a 10 MHz local reference. The local reference is compared with the external clock reference. Software can select the internal or external reference to be driven to the SSMC connector at the bezel. The selected clock is buffered with a 24 mA line driver.

The external 10 MHz is a +7dbm signal [1.416 V pk-pk into 50 ohm load]. The signal is diode protected to 3.3V and ground, terminated with 50 ohms, and compared with a .9V reference. The FLASH 1.8V reference is used along with local division and filtering to insure a quiet reference for this signal. The reference can be changed if necessary.

The local 10 MHz is supplied to a counter in parallel with a second counter referenced to the external 10 MHz. The software can reset, start, and set the end count for the internally referenced counter. For example the software can set a count corresponding to 1 mS of time counting. In addition upper and lower limits can be programmed. At the end of the test the value counted is checked against the limits and status is generated. Passing status is between the limits. The compared values and end counts are buffered and synchronized to allow changes to happen at any time. The value changes are implemented synchronicity as well. The new values will be applied at the next opportunity for a check etc.

LM81 is a monitor circuit controlled with the SMB bus. The FPGA converts the SPI bus to SMB format. The LM81 is initialized for operation and then interrogated for Voltage levels, Fan speeds, and temperature. The device uses A/D´s to load the conversion values into memory. The LM81 stops updating when a value is read. It takes the better part of a second to update again. It is best to do a burst read of any values you are interesting in and then wait for the system requirement before doing it again. The LM81´s can be programmed with upper and lower limits for each of the measurements and alarms generated if the values are out of bounds. Three LM81´s are utilized to have enough voltage inputs for all of the signals to be monitored.

The VPX interface supplies 5V and 3.3V to VPX-GLIB. The 3.3V is used to run the supervisor circuit. When the 3.3V is within range the Reset signal is released to allow the FPGA to operate. This does not affect FPGA loading directly. However, the FPGA won't load properly if the 3.3V is not present since it is used for that process as well.

EXT-GPIO is a bidirectional single ended LVTTL signal. The signal defaults to input and can be controlled via the SPI interface to be an output.

A second GPIO signal is provided with an LVDS buffer. Also programmable to operate as a receiver or transmitter with SW control.

TMP-421 is a remote junction temperature inteface with an SMB connection. Internal and external temperatures are available. The SPI bus can be used to initiate initialization which loads some operating parameters from the internal FPGA registers to the TMP-421.

A second command causes a read of the device. The read polls the device to determine when a cycle has completed [Busy is(becomes) active busy becomes not active] and then read the local and external temperatures and stores those. Status is provided to allow the attached CPU to know when the new values are available. The device ID is returned at the end of initialization.

The received single ended Blanking signals are converted presented to the FPGA. The signals can be scaled with resistors coupled with shunts to reduce higher level signals. The signal path is FUSE - 4.7K - 1K - 1K pulldown - diode protection - comparator. The shunts allow the 4.7K and 1K series resistors to be eliminated. The comparator is referenced via a POT to allow SW to further scale when/how to respond to Blanking inputs.

The POT is programmed via the FPGA SPI path. The references are set to 0 & 3.3V. There are 256 taps. The reference is therefore D/256 * 3.3V with a small offset. A testpoint is provided for the Blanking reference to allow checking of the programmed value. The ATP sets the POT to receive the Blanking inputs and provides a ramp for scope checking.

LVDS IO are provided for the output side of the blanking. These are hardwired to transmit.

Two sets of LVDS to 485, 485 to LVDS IO translation are provided. These IO default to the system standard and can be redefined in SW to reverse direction.

CAL MOD SW is expected to be an LVDS signal and is hardwired to be received. The signal is routed to the FPGA.

Several of the transceivers are programmable for direction and in turn have programmable termination support. The terminations are set to 100 ohms with a 200 MHz rated analog switch to control the connection. Each switch is protected with a diode to prevent active differential pairs from "self powering" the GLIB.

For test purposes PMC-BiSerial-VI was mounted to PCIeBPMCX1 and connected via SCSI cable through the PCIe8LSwVPX3U to interface with the VPX J2/P2 connector. The BiSerial creates the SPI bus and drives/receives the differential and single ended signals. In addition we use an IP-Debug-IO to mount voltage dividers to the rear of the BiSerial to provide the references to the LM81 devices.

If your situation demands a custom application we will update the Xilinx FPGA and IO components. Send us your timing and we will send you the interface. See Models section for currently available versions

email us your wish list or call today

The FPGA is a Spartan VI LX25. The FPGA can be reprogrammed via JTAG to add new features. We mount to PCIe8LSwVPX3U for test and programming purposes. Most of the differential IO is programmable for direction and termination allowing for direction changes etc.

The FPGA receives 50 MHz from the oscillator. The clock input is doubled to 100 MHz and used locally for decoding SPI signaling and operating miscellaneous state-machines.

A TCXO oscillator provides a 10 MHz local reference. The local reference is compared with the external clock reference. Software can select the internal or external reference to be driven to the SSMC connector at the bezel. The selected clock is buffered with a 24 mA line driver.

The external 10 MHz is a +7dbm signal [1.416 V pk-pk into 50 ohm load]. The signal is diode protected to 3.3V and ground, terminated with 50 ohms, and compared with a .9V reference. The FLASH 1.8V reference is used along with local division and filtering to insure a quiet reference for this signal. The reference can be changed if necessary.

The local 10 MHz is supplied to a counter in parallel with a second counter referenced to the external 10 MHz. The software can reset, start, and set the end count for the internally referenced counter. For example the software can set a count corresponding to 1 mS of time counting. In addition upper and lower limits can be programmed. At the end of the test the value counted is checked against the limits and status is generated. Passing status is between the limits. The compared values and end counts are buffered and synchronized to allow changes to happen at any time. The value changes are implemented synchronicity as well. The new values will be applied at the next opportunity for a check etc.

LM81 is a monitor circuit controlled with the SMB bus. The FPGA converts the SPI bus to SMB format. The LM81 is initialized for operation and then interrogated for Voltage levels, Fan speeds, and temperature. The device uses A/D´s to load the conversion values into memory. The LM81 stops updating when a value is read. It takes the better part of a second to update again. It is best to do a burst read of any values you are interesting in and then wait for the system requirement before doing it again. The LM81´s can be programmed with upper and lower limits for each of the measurements and alarms generated if the values are out of bounds. Three LM81´s are utilized to have enough voltage inputs for all of the signals to be monitored.

The VPX interface supplies 5V and 3.3V to VPX-GLIB. The 3.3V is used to run the supervisor circuit. When the 3.3V is within range the Reset signal is released to allow the FPGA to operate. This does not affect FPGA loading directly. However, the FPGA won't load properly if the 3.3V is not present since it is used for that process as well.

EXT-GPIO is a bidirectional single ended LVTTL signal. The signal defaults to input and can be controlled via the SPI interface to be an output.

A second GPIO signal is provided with an LVDS buffer. Also programmable to operate as a receiver or transmitter with SW control.

TMP-421 is a remote junction temperature inteface with an SMB connection. Internal and external temperatures are available. The SPI bus can be used to initiate initialization which loads some operating parameters from the internal FPGA registers to the TMP-421.

A second command causes a read of the device. The read polls the device to determine when a cycle has completed [Busy is(becomes) active busy becomes not active] and then read the local and external temperatures and stores those. Status is provided to allow the attached CPU to know when the new values are available. The device ID is returned at the end of initialization.

The received single ended Blanking signals are converted presented to the FPGA. The signals can be scaled with resistors coupled with shunts to reduce higher level signals. The signal path is FUSE - 4.7K - 1K - 1K pulldown - diode protection - comparator. The shunts allow the 4.7K and 1K series resistors to be eliminated. The comparator is referenced via a POT to allow SW to further scale when/how to respond to Blanking inputs.

The POT is programmed via the FPGA SPI path. The references are set to 0 & 3.3V. There are 256 taps. The reference is therefore D/256 * 3.3V with a small offset. A testpoint is provided for the Blanking reference to allow checking of the programmed value. The ATP sets the POT to receive the Blanking inputs and provides a ramp for scope checking.

LVDS IO are provided for the output side of the blanking. These are hardwired to transmit.

Two sets of LVDS to 485, 485 to LVDS IO translation are provided. These IO default to the system standard and can be redefined in SW to reverse direction.

CAL MOD SW is expected to be an LVDS signal and is hardwired to be received. The signal is routed to the FPGA.

Several of the transceivers are programmable for direction and in turn have programmable termination support. The terminations are set to 100 ohms with a 200 MHz rated analog switch to control the connection. Each switch is protected with a diode to prevent active differential pairs from "self powering" the GLIB.

For test purposes PMC-BiSerial-VI was mounted to PCIeBPMCX1 and connected via SCSI cable through the PCIe8LSwVPX3U to interface with the VPX J2/P2 connector. The BiSerial creates the SPI bus and drives/receives the differential and single ended signals. In addition we use an IP-Debug-IO to mount voltage dividers to the rear of the BiSerial to provide the references to the LM81 devices.

If your situation demands a custom application we will update the Xilinx FPGA and IO components. Send us your timing and we will send you the interface. See Models section for currently available versions

email us your wish list or call today

VPX-GLIB Features

Size

VPX 3U 4HP 160mm x 100mm nominal. Low profile components on rear

IO

10 MHz reference via SSMC at bezel. P2/J2 interface used for SPI, Voltage inputs, Fan speed inputs, Blanking single ended inputs and LVDS outputs, GPIO single ended and differential, remote temperature sensor, and misc. IO. Differential routing with matched length and impedance control where appropriate.

Clocks

50 MHz oscillator , 100 MHz internal, 10 MHz TCXO, External 10 MHz input, 10 MHz reference output. ( other frequencies available), Counters / Dividers / DCM for local clock control.

Interface Types

Custom programmed interfaces are available. Please send us a timing diagram, and we can program one for you. Most interfaces can be adapted from our large library of designs within 2-3 weeks including the updated VHDL, Windows or Linux or VxWorks Driver, reference manuals etc. We can support on-site [ours] integration to help you get your application level software working.

Alternatively choose one of the already completed versions and purchase off-the-shelf. Common requested and implemented interface types include: Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. Mix and Match. Just like but different...

Alternatively choose one of the already completed versions and purchase off-the-shelf. Common requested and implemented interface types include: Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. Mix and Match. Just like but different...

Memory

Spartan 6 - 25 is standard and has 52x1Kx16 BRAM´s to create RAM, FIFO etc.

Software Interface

Control registers are read-writeable via SPI bus.

Interrupts

Attention Line not supported with base model. One of the IO could be redefined for this purpose.

Power Requirement

+5V, +3.3, +12 used and converted to 2.5, 1.2 with local efficient DC:DC power supplies. 1.8V for FLASH with linear regulator.

LED´s

On front indicating Main FPGA voltage [1.2V] is in regulation.

Volatility

Statement of Volatility - all electronics reloaded and reset at power on. All register data lost with power off. No non-volatile memory other than FPGA FLASH.

Reliability

TBD million hours. Bellcore. GB 25c

VPX-GLIB Benefits

Purpose

VPX-GLIB can offload your CPU and reduce board count. VPX-GLIB is a "Kitchen Sink" kind of design providing a lot of the glue logic, electrical format translation, and status features any system needs. For example, the complex interaction required for the remote temperature function is done mainly in HW requiring only a read request and then polling until the new data is available.

Price

System level cost is best when reasonably priced reliable hardware is used and NRE minimized. With VPX-GLIB, reference software, reliable operation, and fantastic client support your cost per unit and overall costs are attractive.

Ease of Use

VPX-GLIB is designed to be easy to use. Direct access to all features, aligned registers for larger access types, programmable features to allow personalization for your system. Please download the manuals and see for yourself. Reference software is provided in source form to get you started. The SW is what we use for test and demonstrates interaction with all features.

Availability

This product is built to order [due to the number of potential customized features]. Dynamic Engineering builds VPX-GLIB on our own SMT line for rapid response. Lead times are generally a few weeks.

VPX Specification Compatibility

VPX-GLIB is compliant per the VITA VPX specifications [61, 48.2]. Tested with PCIe8LSwVPX3U carriers and system simulation card based on PMC BiSerial VI. All Dynamic Engineering VPX Modules are compatible with the PCIe8LSwVPX3U, VPX-GLIB will operate with any VPX specification compliant mother board.

Part Number: VPX-GLIB

Ordering Options

- VPX-GLIB Standard board - Industrial temperature components.

- -ROHS Use ROHS processing. Standard processing is ""leaded"

- -CC Option to add Conformal Coating

- -CC2 Option to add Wedge Locks for conduction cooled model. Retains SSMC and is not supplied with Bezel.

- -XXX See Manuals section for customized versions and replace XXX with type or create your own "Client Number"

VPX-GLIB

Software Support. Since VPX-GLIB does not have a PCIe interface, the Base model has reference software from our testing based on the PMC BiSerial VI. Any new versions will be tested in a similar way and the reference SW from those efforts can be used to help with integration in your system.

Dynamic Engineering has expertise with Windows, Linux, VxWorks and other OS for Drivers and Reference SW development.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Dynamic Engineering has expertise with Windows, Linux, VxWorks and other OS for Drivers and Reference SW development.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

VPX-GLIB Models

VPX-GLIB base model

Customer: JEDS

Base version from description tab.

Download the VPX-GLIB Hardware manual.

Customer: JEDS

Base version from description tab.

Download the VPX-GLIB Hardware manual.