DHTML JavaScript Website Pull Down Navigation Menu By Milonic

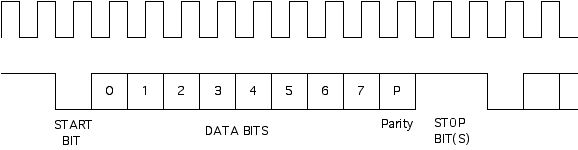

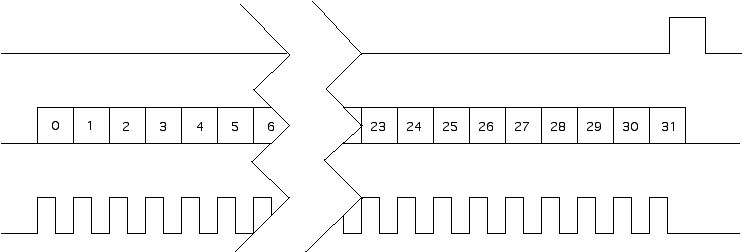

PMC-BiSerial-BA1 PMC Compatible Bus Data Analyzer with two protocols The BA1 protocol implemented provides a Serial Data Analyzer function used for network snooping in a test environment. -32 FIFO option.Please note that the PMC-BiSerial has been upgraded and the PMC-BiSerial-III is currently recommended for new designs

Custom interfaces are available. We will redesign the state machines and create a custom interface protocol. That protocol will then be offered as a standard special order product. Please see our web page for current protocols offered. Please contact Dynamic Engineering with your custom application. email us your wish list or call today! Related Products: 68 position terminal strip to SCSI III connector adapter and BiSerial compatible SCSI III cable PMC-BIS-Eng-Kit..........Engineering Kit for PMC-BiSerial includes Board level Schematics [PDF], Reference Software [WIN NT, WinRT, Visual C ZIP file], HDEterm68-MP, HDEcabl68You must have Adobe Acrobat to read our PDF files. PMC-BiSerial-BA1 manual PDF .Custom, IP, PMC, PC*MIP, PCI, VME Hardware, Software designed to your requirements Home |

News |

Search the Dynamic Engineering Site

[an error occurred while processing this directive]