IP-QuadUART-485

IP Module with 4, RS-485 UARTs

Order This Item

IP-QuadUART Description

- Driver included with purchase

- Standard Type II module

- 8↔32 MHz. operation

- 4 UART ports per IP with TX, RX, RTS, CTS, DSR, DTR signals per Port

- 24 MHz and 18.432 Mhz oscillators to reference UART

- RS-485 Full and Half Duplex operation

- 8, 16, 32 bit data support for more efficient transfer

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature option.

- ROHS and Standard processing available

IndustryPack® Modules are an important part of solutions for Embedded situations. Rugged, small, light .. just right for many applications. With IP-QuadUART-485 many communications, telemetry, command and control applications can be handled.

The IndustryPack compatible IP-QuadUART-485 design integrates a quad UART onto an IndustryPack module. The UART (16C854) features 128 byte FIFOs for RX and TX ports on each channel. The UART is supported by an advanced IP module interface implemented within a Xilinx FPGA.

UART is a character based interface [8 bits]. The IndustryPack interface has several features which optimize performance. Words can be written to IP-QuadUART-485 and the data will be converted to bytes before being sent to the UART. The IP interface will latch the data allowing the host computer to be released while the data is being moved to the UART. The early release allows pipelined operation and increased performance. When IP-QuadUART-485 is mounted to a carrier which supports 32 bit operations the effect can be enhanced. PCI3IP, PCI5IP , cPCI4IP and cPCI2IP and other Dynamic Engineering carriers support 32 bit access to IndustryPacks.

When reading data, IP-QuadUART-485 supports 8, 16, and 32 bit accesses by assembling the bytes read from the UART into a register within the Xilinx. With 32 bit reads 1/4 of the data transfer cycles are needed. In the standard mode the data is read when the host performs the transfer cycle. An optional higher performance mode of operation is the pre-read mode. In pre-read the UART is read and the data stored within the Xilinx. With the data stored internal to the Xilinx the data can be accessed without waiting for the UART.

IP-QuadUART-485 is compatible with 8 and 32 MHz IP bus interfaces. A speed select control bit optimizes the state machine for either frequency.

IP-QuadUART-485 is compatible with RS-422 / RS-485 requirements. Software can select full or half duplex operation on each port independently. Supported signals are [RX, TX, CTS, RTS, DSR, DTR]. Software has control over the output drivers ito allow multi-drop operation.

The UART IO is available at the IO connector. Most IP carriers route the IP module IO connectors to 50 pin headers to support ribbon cable. The HDRterm50 can be used to create a terminal block interface.

Two local oscillators are provided to allow the full range of the UART to be utilized. 24 MHz and 18.432 Mhz oscillators provide 1.5 M max rate with RS-422 and all of the standard baud rates . The 32 MHz IP clock can be selected to operate up to 2 MHz.

The IP Module driver can be instantiated multiple times to control multiple cards by the same CPU. IP-QuadUART-485 when coupled with the Dynamic Driver "knows" what slot it is in and which carrier it is installed into. The slot and carrier information is required when using multiple cards in a PCI/PCIe/VPX etc. system with dynamic address assignment. A known system configuration can be combined with the slot and carrier information to deterministically access the right device.

IndustryPack® Modules require a "carrier" in most cases to adapt them to the system. Dynamic Engineering has carrier solutions for a variety of formats.

PCIe implementations can be done with the PCIe3IP and PCIe5IP.

PCI implementations can be done with the PCI3IP and PCI5IP.

cPCI 3U is supported with the cPCI2IP. Up to 2 IP-QuadUART-485 per slot

cPCI 6U is supported with the cPCI4IP. Up to 4 IP-QuadUART-485 per slot

PC104p is supported with the PC104pIP.

PC104p situations with a custom mechanical can be done with the PC104p4IP. Up to 4 IP-QuadUART-485 per slot

VPX 3U is supported with the VPX2IP. Up to 2 IP-QuadUART-485 per slot

The IndustryPack compatible IP-QuadUART-485 design integrates a quad UART onto an IndustryPack module. The UART (16C854) features 128 byte FIFOs for RX and TX ports on each channel. The UART is supported by an advanced IP module interface implemented within a Xilinx FPGA.

UART is a character based interface [8 bits]. The IndustryPack interface has several features which optimize performance. Words can be written to IP-QuadUART-485 and the data will be converted to bytes before being sent to the UART. The IP interface will latch the data allowing the host computer to be released while the data is being moved to the UART. The early release allows pipelined operation and increased performance. When IP-QuadUART-485 is mounted to a carrier which supports 32 bit operations the effect can be enhanced. PCI3IP, PCI5IP , cPCI4IP and cPCI2IP and other Dynamic Engineering carriers support 32 bit access to IndustryPacks.

When reading data, IP-QuadUART-485 supports 8, 16, and 32 bit accesses by assembling the bytes read from the UART into a register within the Xilinx. With 32 bit reads 1/4 of the data transfer cycles are needed. In the standard mode the data is read when the host performs the transfer cycle. An optional higher performance mode of operation is the pre-read mode. In pre-read the UART is read and the data stored within the Xilinx. With the data stored internal to the Xilinx the data can be accessed without waiting for the UART.

IP-QuadUART-485 is compatible with 8 and 32 MHz IP bus interfaces. A speed select control bit optimizes the state machine for either frequency.

IP-QuadUART-485 is compatible with RS-422 / RS-485 requirements. Software can select full or half duplex operation on each port independently. Supported signals are [RX, TX, CTS, RTS, DSR, DTR]. Software has control over the output drivers ito allow multi-drop operation.

The UART IO is available at the IO connector. Most IP carriers route the IP module IO connectors to 50 pin headers to support ribbon cable. The HDRterm50 can be used to create a terminal block interface.

Two local oscillators are provided to allow the full range of the UART to be utilized. 24 MHz and 18.432 Mhz oscillators provide 1.5 M max rate with RS-422 and all of the standard baud rates . The 32 MHz IP clock can be selected to operate up to 2 MHz.

The IP Module driver can be instantiated multiple times to control multiple cards by the same CPU. IP-QuadUART-485 when coupled with the Dynamic Driver "knows" what slot it is in and which carrier it is installed into. The slot and carrier information is required when using multiple cards in a PCI/PCIe/VPX etc. system with dynamic address assignment. A known system configuration can be combined with the slot and carrier information to deterministically access the right device.

IndustryPack® Modules require a "carrier" in most cases to adapt them to the system. Dynamic Engineering has carrier solutions for a variety of formats.

PCIe implementations can be done with the PCIe3IP and PCIe5IP.

PCI implementations can be done with the PCI3IP and PCI5IP.

cPCI 3U is supported with the cPCI2IP. Up to 2 IP-QuadUART-485 per slot

cPCI 6U is supported with the cPCI4IP. Up to 4 IP-QuadUART-485 per slot

PC104p is supported with the PC104pIP.

PC104p situations with a custom mechanical can be done with the PC104p4IP. Up to 4 IP-QuadUART-485 per slot

VPX 3U is supported with the VPX2IP. Up to 2 IP-QuadUART-485 per slot

IP-QuadUART-485 Features

Size

1.8 x 3.9 inches nominal Type II with low profile components on rear

IO

Each of the 4 UART ports can be selected full and half duplex operation with software. Frequency, data width, partity, stop bits etc. are also programmable per port.

Speed

Porgrammable based on the selected reference and divisor plus system - cable length and quality.

Termination

RX [full duplex], CTS and DSR signals are terminated. Half duplex the RX ports are normally not terminated. Software controlled.

Clocks

Compatible with 8 and 32 MHz IP bus operation. The oscillator frequencies [24 and 18.432] support standard and custom baud rates. Custom versions with special frequency requirements can be supported

Write Access

The write cycle to IP-QuadUART-485 is pipelined with an early termination to the IP host. The pipelining reduces the access time in writing to the UART FIFO memory. Byte expansion from words is supported.

Read Access

Read cycles wait for data to be available from the UART or can be selected to pre-read the data to support higher performance operation. Byte packing into words is supported.

Software Interface

Control registers are read-writeable

IO, ID, INT spaces supported.

Windows®, Linux reference SW and Drivers

IO, ID, INT spaces supported.

Windows®, Linux reference SW and Drivers

Interrupts

Interrupt level 0 is used to route the QuadUART interrupt to the host computer. The interrupt is maskable and pollable.

Power Requirement

+5V approximately 200 mA max.

Volatility

Statement of Volatility

Reliability

BellCore 25C GB 1,620,017 Hours

IP-QuadUART-485 Benefits

Speed

Price

System level cost is best when reasonably priced reliable hardware is used and NRE minimized. With IP-QuadUART-485, driver support for the carrier and IP level, reference software, history of reliable operation, and fantastic client support your cost per unit and overall costs are attractive. Another aspect of cost is the cost of change when your card goes obsolete. Dynamic Engineering is committed to keeping our product line available as long as possible for our clients. IP-QuadUART-485 was introduced in 2002. Updated as necessary with changes hidden by the FPGA.

Ease of Use

IP-QuadUART-485 is designed to be easy to use. Direct access to all FPGA based features, [UART features defined by industry standard UART interface] aligned registers for larger access types, programmable features to allow personalization for your system. Please download the manuals and see for yourself. Reference software is provided in source form to get you started. Standard 16550 type UARTs allow recompiliation of 3rd party SW "only" needing the local addresses defined.

Availability

IP-QuadUART-485 is a "stocked" item. This means IP-QuadUART-485 is either in stock or has a short lead time depending on your order size and other recent orders.

IP Specification Compatibility

IP-QuadUART-485 is compliant per the VITA 4 - 1995 specification. Tested with PCI and PCIe based carriers. All Dynamic Engineering IP Modules are compatible with PCIe3IP, PCIe5IP, VPXI2IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP etc. IP-QuadUART-485 will operate with any IP specification compliant carrier board.

Part Number: IP-QuadUART-485

Ordering Options

- IP-QuadUART-485 Standard board - with RS-422/485 programmable IO.

- -ROHS Use ROHS processing. Standard processing is ""leaded"

- -CC Option to add Conformal Coating

- -XXX See Models section for predefined versions and replace XXX with type

- Types

IP-QuadUART-485 Drivers

Software Support for IP-QuadUART-XXX includes: Windows, and Linux compliant drivers

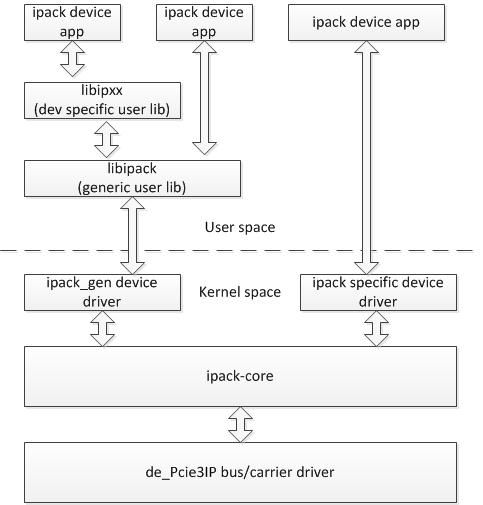

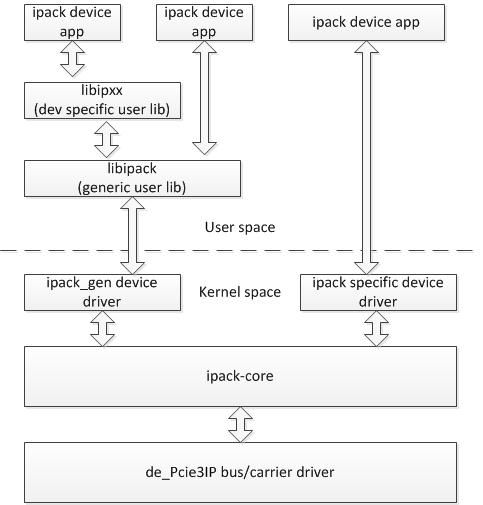

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of IP-QuadUART-485 implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type / version of IP-QuadUART-485 implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

IP-QuadUART-485 predefined models

Click on the links to Download selected manuals in PDF format.

Base Model 4 UART interfaces coupled with programmable IO for RS-485, and RS-422 applications.

Standard Model Hardware Manual

Standard Model Windows Manual

Base Model 4 UART interfaces coupled with programmable IO for RS-485, and RS-422 applications.

Standard Model Hardware Manual

Standard Model Windows Manual