ccPMC-HOTLINK

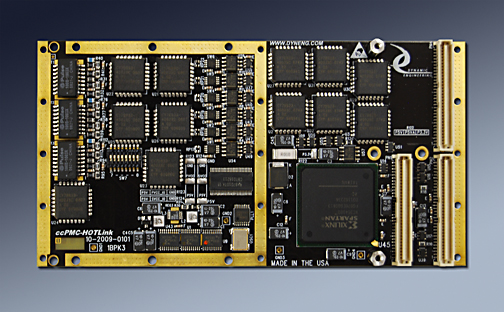

Conduction Cooled PMC Format

Shown with Transformer option

| Single wide ccPMC. |

|

| |

|

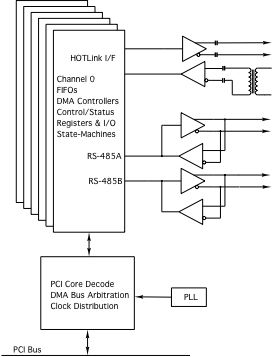

| 6 independent Bidirectional PECL based HOTLink channels. Impedance controlled differentially routed channels. |

|

| |

|

| 6 pairs of RS485/LVDS IO can be allocated 2 per HOTLink channel or used as a separate function with 12 available. 40/200 MHz IO, matched length, differentially routed with controlled impedance. Programmable terminations and options for tristate [pull-up/pulldown] control. |

|

| |

|

| Pn4 backplane connection. Your PMC carrier will specify the system connector. |

|

| |

|

| Channelized design with repeating common offsets for registers in each channel. DMA and direct access to FIFO´s attached to HOTLink IO. Drivers available for Windows® , with options for Linux, VxWorks or detailed hardware / memory map information in HW manual [download at the bottom of this page] for user designed drivers. Reference software using the Dynamic Drivers is available. |

|

| |

|

| The HOTLink board supports various interrupts. All interrupts are individually mask´able and a channel master interrupt enable is provided to disable all interrupts on a channel simultaneously. The current real-time status is also available making it possible to operate in a polled mode. |

|

| |

|

| +3V, +5V |

|

| All bits are routed through the FPGA to allow for custom state-machine implementations. FIFO and Dual Port RAM can be implemented. See custom models below. |

|

| |

|

| Download PDF here |

| Your time to market will be shortened by the easy to use interface, flexibility in design, and off-the-shelf availability. ccPMC-HOTLink is a software controlled HW interface. With DMA enabled and FIFO´s instantiated fast transfers can occur. Each channel has a separate DMA controller to allow for high speed large transfers without SW intervention required. |

|

| |

|

| ccPMC-HOTLink has an attractive price, and low integration cost for a low system cost. ccPMC-HOTLink can be used with PIM Universal and PIM Carrier in cPCI environments. An integrated rear IO transition solution with your specific connector requirements can be designed for you. Please contact Dynamic Engineering about your IO requirements. |

|

| |

|

| ccPMC-HOTLink is easy to use. A point and shoot user interface to the IO. Please download the manual and see for yourself. The engineering kit provides a good starting point for a new user. The drivers [Windows® or Linux] come with reference software demonstrating DMA, register and memory accesses, PLL programming utilities and loop-back tests. The reference software is in source form and can be used for your design. Modify away. |

|

| |

|

ccPMC-HOTLink is designed to be customized. The base version is available from stock. New clientizedversions can be dialed in quickly. We can ship a model that is just like but differentto you right away and follow-up with new FLASH files to match your requirements. You can make a quick start having the HW available right away and adding features as they are available. |

|

| |

|

| ccPMC-HOTLink is a standard single wide ccPMC [single slot] board which conforms to the ccPMC mechanical and electrical specifications. Eliminate mechanical interference issues. |

|

| |

|

| ccPMC-HOTLink is PMC compliant per the IEEE 1386 specification. ccPMC-HOTLink is also compliant with the conduction cooled PMC specification. | |

| |

|

| ccPMC-HOTLink is PCI compliant. You can develop with a PCIe to PMC adapter - PCIeBPMCX1 or 2 position PMC Mini Carrier etc.. |

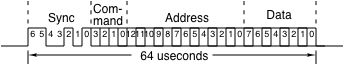

Base Transmit Request Timing

Base Transmit Request Timing