## DYNAMIC ENGINEERING

150 DuBois Street Suite B&C Santa Cruz, CA 95060 831-457-8891 <a href="https://www.dyneng.com">https://www.dyneng.com</a> sales@dyneng.com Est. 1988

## cPCI2IP

## **User Manual**

Integrated cPCI  $\Leftrightarrow$  IP Module Carrier

## **Key Features**

Fast Access with integrated PCI ⇔ IP Bridge

2 IP Positions with IO

8/32 MHz IP operation

8/16/32 bit accesses supported

16/32 bit IP module support

Data Alignment – Byte and Word Swapping

Watch Dog Timer

LED's - Power, IP Access, User

Multi-board support

Manual Revision 5p3 12/19/23 Corresponding Hardware: Revision 10-2002-0805 Firmware Revision 7p4 Dynamic Engineering 150 DuBois Street Suite B&C Santa Cruz, CA 95060 831-457-8891

This document contains information of proprietary interest to Dynamic Engineering. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to ensure that this manual is accurate and complete. Still, the company reserves the right to make improvements or changes in the product described in this document at any time and without notice. Furthermore, Dynamic Engineering assumes no liability arising out of the application or use of the device described herein.

The electronic equipment described herein generates, uses, and can radiate radio frequency energy. Operation of this equipment in a residential area is likely to cause radio interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

Connection of incompatible hardware is likely to cause serious damage.

©1988-2023 by Dynamic Engineering.

Other trademarks and registered trademarks are owned by their respective manufactures.

# **Table of Contents**

| PRODUCT DESCRIPTION                                                                                         |                            |  |

|-------------------------------------------------------------------------------------------------------------|----------------------------|--|

| THEORY OF OPERATION                                                                                         | 11                         |  |

| INSTALLATION                                                                                                | 12                         |  |

| ADDRESS MAP                                                                                                 | 13                         |  |

| PROGRAMMING                                                                                                 | 14                         |  |

| Register Definitions  cPCI2IP_intreg_base  cPCI2IP_intreg_(a-b)  cPCI2IP_intreg_int  cPCI2IP_intreg_dswitch | 16<br>16<br>18<br>21<br>23 |  |

| APPLICATIONS GUIDE                                                                                          | 24                         |  |

| Interfacing Engineering Kit                                                                                 | <b>24</b> 25               |  |

| J2 IP MODULE IO PIN ASSIGNMENT                                                                              | 26                         |  |

| Construction and Reliability                                                                                | 27                         |  |

| MTBF                                                                                                        | 27                         |  |

| Thermal Considerations                                                                                      | 27                         |  |

| WARRANTY AND REPAIR                                                                                         | 28                         |  |

| Service Policy Out of Warranty Repairs                                                                      | <b>29</b><br>29            |  |

| For Service Contact:                                                                                        | 29                         |  |

| SPECIFICATIONS    | 30 |

|-------------------|----|

| ORDER INFORMATION | 31 |

# List of Figures

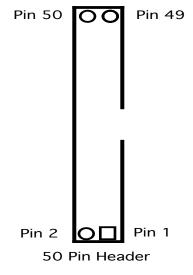

| FIGURE 1  | CPCI2IP POWER FILTERING         | 8  |

|-----------|---------------------------------|----|

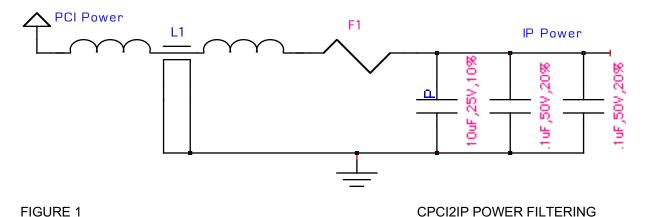

| FIGURE 2  | CPCI2IP RESET CIRCUIT           | 9  |

| FIGURE 3  | CPCI2IP STROBE CONNECTION TABLE | 10 |

| FIGURE 4  | CPCI2IP ADDRESS MAP             | 13 |

| FIGURE 5  | CPCI2IP CONTROL PORT            | 16 |

| FIGURE 6  | CPCI2IP SLOT CONTROL PORT       | 18 |

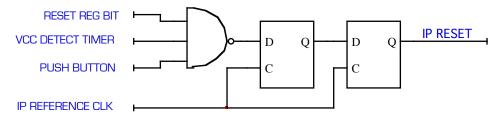

| FIGURE 7  | CPCI2IP 16 BIT BYTE SWAPPING    | 19 |

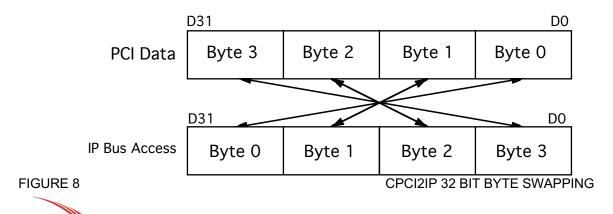

| FIGURE 8  | CPCI2IP 32 BIT BYTE SWAPPING    | 19 |

| FIGURE 9  | CPCI2IP INTERRUPT STATUS PORT   | 21 |

| FIGURE 10 | CPCI2IP USER SWITCH PORT        | 23 |

| FIGURE 11 | CPCI J2 PIN ASSIGNMENT          | 26 |

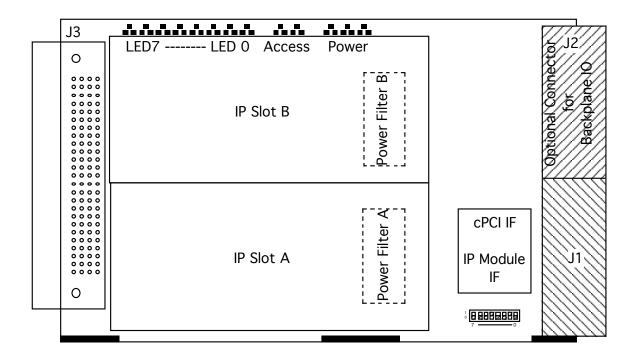

| FIGURE 12 | CPCI2IP CONNECTOR REFERENCE     | 32 |

## **Product Description**

cPCI2IP is part of the Dynamic Engineering IP Compatible family of modular I/O components. cPCI2IP provides two IndustryPack® Compatible sites in one cPCI position. The pair can be used for double wide IP Modules with either 16 or 32 bit IP Module bus.

ID, IO, INT, and MEM access types are supported for read and write cycles. The full 8 Mbytes of address space is allocated to each of the MEM spaces.

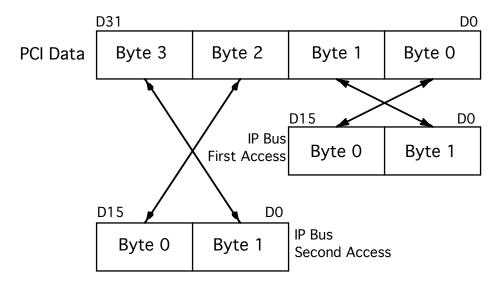

The cPCI bus is 32 bits wide and most industry packs are 16 bit devices. Byte, word, and long word accesses are supported. Bytes can be to any address. Word accesses need to be word aligned. Long word accesses need to be long word aligned. Each of the access types has a one-to-one correspondence to the hardware. There are no "extra" accesses with the cPCI2IP design.

The Data bus is designed as a 32-bit bus with slot B on the D15-0 segment. A is on the D31-16 half of the bus. The current hardware compensates and allows for standard accesses to all slots – software transparent. The AB slot can be accessed as a 32 bit wide data path. The AB slots are mechanically aligned for double wide card installation as well as pairs of single wide cards.

A long word access to a 16 bit port will automatically be converted into two back-to-back IP accesses with the address incrementing between cycles unless the increment disable function is selected (see Slot control register description). In the increment disable case the hi or low address can be specified for the double access.

For a read, one 32 bit data word will be returned. For example a long word read to the ID space would yield \$xx50xx49 for many boards as the "0" location has \$49 and the next address has \$50. The long word mode happens automatically when all 4 of the byte lane enables are detected asserted. The overall throughput is greatly enhanced with this mode of operation. Please note that the non-data bytes should be masked, as many IP's do not drive the "off byte".

For a long word access to a long word port the 32 bit IP data bus is utilized. Slot AB forms a 32 bit slot when 32 bit IPs are installed. The access type is automatic based on the address space used to access the slots. You can use 16 and 32 bit accesses intermixed without changing your control registers if the IP supports both. Slot B control register defines the access when in 32 bit mode. It may be necessary to match Slot A clock to slot B if your IP uses both.

The address is shifted from long [32] to short [16] by hardware and the byte strobes used to access the individual bytes or words. If your card has mixed addressing requirements you may need dual defines to account for the 32 bit and 16 bit addressing.

The PCI bus is defined as little endian and many IPs have their register sets defined to operate efficiently with a little endian interface. The default settings on the cPCI2IP are "straight through" byte for byte and D15-0 written to address 0x00 before D31-D16 written to address 0x02 when long words are written to 16 bit ports. Please note that any long word address can be used. The lower data is written to the lower address first, then the upper data to the upper address. Each slot has a BS and WS control bit to allow Byte and Word Swapping to be performed to accommodate alternate IP and OS requirements.

#### Byte Swapping

16 bit ports

D15-8 ⇔ D7-0

D31-24 ⇔ D23-16

32 bit ports

D31-24 => D7-0

D23-16 => D15-8

D15-8 => D23-16

D7-0 => D31-24

Word Swapping will swap D31-16 with D15-0

If byte swapping is enabled and 0x1234 is written to an IP slot, then the IP will see 0x3412. If 0x12345678 is written to a 32-bit port then the IP will see 0x78563412. The "is written" is defined by the data on the PCI bus. Your software/OS may do its own conversion before the data gets to the PCI bus.

The byte and word swap controls are separated to allow the conversion to be used for big-little endian and for register mapping purposes. Each slot has separate controls for access to that slot.

The cPCI2IP has a watch-dog timer function which completes the IP access if the IP does not respond within 7.6 uS. The watch-dog timer has a master status bit and an optional interrupt output. In addition to the master status each slot control register reports status for the bus error. Multi-threaded programs can tell if their hardware access caused the Bus Error even if other threads have accessed other hardware since the bus error was caused.

Each slot is programmable for 8 or 32 MHz. operation. The control register has

separate bits for slots A and B. The clocks are locked together and can be switched at any time. Hardware insures that the clocks switch basis on a clock period boundary to provide seamless operation.

The cPCI2IP supports interrupts from each slot with separate mask bits. Two interrupts from each of the five slots. An interrupt "force" bit is supplied to aid in software development. The bus error [watch dog timer] can also be an interrupt condition. The masked interrupts are tied together and connected to INTA on the PCI bus.

The cPCI2IP has LEDs for power, access, and user functions. The three voltages from slot B are connected to three LEDs. An additional 8 LEDs are supplied which are controlled via the control register for user defined purposes. Two LEDs are controlled by a timer circuit which is activated by the acknowledge from each of the IP slots.

Power to each of the IP slots is individually filtered and fused for +5 and ±12. The fuses are rated at 2A on the 5V rail and 1.1A on the ±12V rails. cPCI2IP is designed to route maximum power to each slot in parallel. The power supply capabilities for your chassis may provide additional constraints. Each slot filter has a separate RF filter, bulk capacitor, "self healing" fuse, and bipass capacitors. A bipass capacitor is located at each of the power pins on the cPCI2IP with the bulk capacitor near the filter pin for optimum noise rejection, voltage hold-up and local filtering.

With the filter pin on each slot and bulk capacitor each IP is effectively isolated from the other IPs mounted to the cPCI2IP. Additional work was done in layout to minimize the amount of cross-slot electronic noise. Each of the IP slots is also isolated from the PCI interface by the power conditioning. The FPGA uses 3.3 and 2.5V power which is derived from the 5V supply and bussed on mini-planes to the FPGA. The FPGA is effectively isolated from the IP slots by the regulators and additional filtering.

cPCI2IP is well behaved with low noise power provided to each of the slots. cPCI2IP is designed for analog and digital IP applications including data acquisition, instrumentation, measurement, command and control, telemetry and other industrial applications.

An 8 bit "dip switch" is provided on cPCI2IP. The switch configuration is readable via a register. The switch is for user defined purposes. We envision the switch being used for software configuration control, PCI board identification or test purposes.

The reset switch provided can be used to reset the IP devices without affecting the PCI bus. Power, PCI reset, and a control register bit also cause the IP Reset to be activated. The reset is controlled to be synchronous to the 8 MHz. clock. Alternatively, the IP-Debug-Bus card can be used for individual slot resets.

FIGURE 2 CPCI2IP RESET CIRCUIT

The cPCI2IP conforms to the VITA standard for IndustryPack Carriers. This guarantees compatibility with multiple IndustryPack compatible modules.

The cPCI2IP conforms to the PCI 2.2 specification and supports both 3.3V and 5V signaling levels. cPCI2IP is accessible in the memory space on the PCI bus. This guarantees compatibility with other cPCI compliant hardware. cPCI2IP is compatible with PICMG 2.0 R 3.0 for the IO definitions when J2 is installed.

The PCI interface is integrated with the IP interface providing superior performance over designs relying on a separate PCI interface device. The higher level of integration results in fewer initialization steps and requirements, more flexibility in operation, a higher MTBF, and less complex software with only one Base Address [BAR] to deal with.

If your project can benefit from a "non-standard" implementation, or features that we have not implemented yet please let us know. The Xilinx has room.

Wired but not yet implemented. (1) All of the DMA control signals are available for a future revision to implement.

Wired and User implemented. The IP Strobe signal is connected from each IP slot to a header to allow for inter-slot user defined communications. The IP specification does not define what the strobe can be used for. The header is rarely used. If you need it please add –stb to your order number and we will install the header for you. Standard .025" sq. posts suitable for wire-wrap inter-connection.

On the IP Slot the Strobe signal is connected to pin 46.

Strobe Pinout on Header

J4

2 STB A 1 STB B

FIGURE 3

CPCI2IP STROBE CONNECTION TABLE

The IO are brought to 50 pin headers [default]. The headers are installed with ejectors for ease of use and retention. The IO are also optionally available at the rear panel [-J2]. The rear panel IO are isolated with  $0\Omega$  resistors located near the IP-IO connectors to minimize the stub length if the rear panel IO is not in use. Some cPCI systems have 64 bit PCI buses which conflict with the rear panel IO. Please check with your system before selection this option.. If using rear panel IO the front bezel has a blank installed left off for better EMI sealing. The –IO option provides both Bezel and J2 IO.

## **Theory of Operation**

The cPCI2IP is used to bridge from cPCI to IP bus specifications. The cPCI bus will be the master in most cases with the IPs being accessed for read or write cycles. The cPCI accesses are handled at the lowest level by the PCI core.

The cPCI bus provides multiplexed address and data plus control lines. The data is separated from the address, and the control lines are decoded to provide the inputs to the IP Interface state machines. The address is tested to determine which slot the access belongs to and which type of access to implement. The IP control strobes are generated. When acknowledge is received the cycle is terminated back to the host. The PCI bus will see a retry mode while the access is taking place and "disconnect with data" when the cycle is completed.

#### **Feature List**

- cPCI Universal Voltage [3.3 or 5V signaling]

- Integrated PCI ⇔ IP conversion for faster access

- 2 IP compatible slots

- Full ID, IO, INT, and Memory space allocated for each slot

- 8 or 32 MHz operation in each slot independently

- byte, word, long word access. 32 bit access to 16 bit slots with static or incrementing address. 32 bit access to 32 bit slots.

- byte and word swapping for little endian big endian conversion

- Bus error abort response with slot status

- Bezel IO 1:1 50 pin headers with .008" traces between IO and header

- J2 IO option with isolation resistors

- IP Reset Switch

- 8 position "DIP Switch" slot identification when multiple cPCI2IPs are in your system or for user defined purpose(s)

- 8 User LEDs, 3 Power LEDs, 2 Access LEDs

- Fused Filtered Power with re-settable "self healing" fuses in each slot.

- Upgrade Program. Get the newly added features with a new PROM.

- Fully compliant injector/ejector handle on cPCI EMC bezel.

- ESD strip per cPCI specifications.

- Windows® Drivers available. Generic IP interface included with driver to support your IP. Dynamic Engineering driver development available for customized IP support. [please download the separate Driver manual]

- Linux Driver.

- Plug and Play operation with Addressing, Interrupts, driver loading for Windows® and other O/S.

The drivers are organized as "Parent" and "Child". The parent drivers are unique to each of the Dynamic Engineering carriers. The Child drivers are portable between any of the Dynamic Engineering carriers. Develop on the PCI3IP and then reuse on the cPCI2IP for example. The portability applies to the Windows and Linux drivers.

As Dynamic Engineering adds features to the hardware we will update the cPCl2IP page on the Dynamic Engineering website. If you want the new features, and have already purchased hardware, we will support you with an update where possible.

The basic PCI identifying information will not change with the updates. The revision field will change to allow configuration control. Current revision is 0x07.

#### Installation

The cPCI2IP and the IPs to be mounted should be treated as static sensitive hardware. The technician should be properly grounded; the mounting and installation process should be performed at a static free workstation.

cPCI2IP can be installed into any non-system cPCI slot with 3U 4HP capability. The bezel securely retains the cPCI2IP within the chassis. cPCI2IP with type1 IP Modules installed is cPCI legal for height, length and width. Adjacent slots can be filled with multiple cPCI2IP cards. With Type II modules, [parts on the rear] in most cases, the combination will still be "single slot".

Each of the IP slots can have an IP installed. IndustryPack®s are installed by pushing the mezzanine card onto the connector pair on the cPCl2IP. Each slot is clearly marked. The IO connector is located near the top of the cPCl2IP and the IP Bus connector near the cPCl backplane connectors. The IP connectors are keyed making orientation error proof. Please refer to Figure 12 for the slot and IO connector placement.

The IP mounting kit can be utilized to secure the IP to the cPCI2IP. Each Dynamic Engineering IP sold comes with a mounting kit. If you need a replacement or your IP comes from another manufacturer please order IP-MTG-HW. 1 kit per IP. The kit includes the mounting hardware – screws and standoffs. https://www.dyneng.com/IPHardware.html

If more than one cPCI2IP is to be installed into the same system – visible on the PCI bus the dipswitch can be set to different positions on each card. Software can use the dipswitch setting to identify which cPCI2IP is allocated which address space and associate specific IP/cables with that cPCI2IP so there is positive automatic control of

your system configuration. The Dynamic Engineering Driver makes use of this feature to allow multiple cPCl2IPs to be used in the same system without identification challenges.

## **Address Map**

| cPCI2IP_intreg_base<br>cPCI2IP_intreg_a<br>cPCI2IP_intreg_b<br>cPCI2IP_intreg_dswitch<br>cPCI2IP_intreg_int      | 0x00000000 // base control register 0x00002000 // slot A specific clock and interrupt 0x00003000 // slot B 0x00006000 // User Switch read back port 0x00007000 // Interrupt status read-back                                                                                               |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cPCl2IP_ida_st<br>cPCl2IP_idb_st<br>cPCl2IP_idab_st                                                              | 0x00140000 // starting addr of slot A ID space 0x00120000 // starting addr of slot B ID space 0x00160000 // starting addr of slot AB ID space                                                                                                                                              |

| cPCl2IP_ioa_st<br>cPCl2IP_iob_st<br>cPCl2IP_ioab_st                                                              | 0x00240000 // starting addr of slot A IO space 0x00220000 // starting addr of slot B IO space 0x00260000 // starting addr of slot AB IO space                                                                                                                                              |

| cPCI2IP_inta_st<br>cPCI2IP_intb_st<br>cPCI2IP_intab_st                                                           | 0x00340000 // starting addr of slot A INT space 0x00320000 // starting addr of slot B INT space 0x00360000 // starting addr of slot AB INT space                                                                                                                                           |

| cPCI2IP_mema_st<br>cPCI2IP_mema_en<br>cPCI2IP_memb_st<br>cPCI2IP_memb_en<br>cPCI2IP_memab_st<br>cPCI2IP_memab_en | 0x00800000 // starting addr of slot A MEM space 0x00ffffff // end address of slot A MEM space 0x01000000 // starting addr of slot B MEM space 0x017fffff // end address of slot B MEM space 0x01800000 // starting addr of slot B MEM space 0x01ffffff // end address of slot AB MEM space |

FIGURE 4 CPCI2IP ADDRESS MAP

The address map provided is for the local decoding performed within cPCl2IP. The addresses are all offsets from a base address. The host the cPCl2IP is installed into provides the base address and interrupt level. Your software will need to concatenate the base address + cPCl2IP address + IP Local address to create a pointer to each programmable feature on your IP.

## **Programming**

The address map will get you to the IP. The IP board description will provide the local addresses. If you are in a Windows or Linux environment you might want to use a Dynamic Engineering Driver for the carrier and IP. Complete information is provided within this manual to allow customers who use another OS or want to write their own interface to do so.

Dynamic Engineering can write a driver for your IP to interface with our carrier(s) even if it is not "one of ours". Please contact <a href="mailto:engineering@dyneng.com">engineering@dyneng.com</a> with your requirements if you are interested in this service.

The host system will search the cPCI bus to find the assets installed during power-on initialization. The Vendorld = 0x10EE and the CardId = 0x0011 for the cPCI2IP. Interrupts are requested by the configuration space. Third party utilities can be useful to see how your system is configured. The Vendorld and CardId parameters are used by the OS to identify the card and in some cases launch the plug and play installation process. The interrupt level expected and style is also set in the registry.

Once the initialization process has occurred and the system has assigned an address range to the cPCI2IP card, the software will need to determine what the address space is. We refer to this address as base0 in our software.

The next step is to initialize the cPCI2IP. The default of no interrupts enabled and 8 MHz. operation will be valid in many cases. The base register for the cPCI2IP and specific slot registers A,B can be initialized to change the default parameters to suite your requirements. Please refer to the register map definitions for more information.

Access to your installed IP is done by accessing base0 + slot address + IP offset. The slot address is defined in the memory map. For example to read your IP in slot B IO space: \*(base0 + cPCI2IP\_iob\_st + ip offset) = data. Each slot and memory type [IO, ID, INT, Mem] has a unique address space for 12 defined address spaces plus the cPCI2IP internal address space. The internal registers are defined in the following pages.

The cPCI2IP has an integrated PCI interface with IP bridge. The integrated approach simplifies programming with only one base address and fewer parameters to have to initialize. The integrated approach is also faster access creating higher performance in your system.

Higher performance for your system can be achieved by matching the IP register model to the OS and user software model that you are using, selecting the optimal IP

reference clock rate and access types.

The cPCI2IP has individual clock selection for each of the IP Slots. The access time is reduced when the IP clock rate is set to 32 MHz. The cPCI2IP can handle any mixture of clock requirements. Make sure that the IP in the slot can handle the higher rate.

The cPCI2IP can handle byte, word and long word accesses from the PCI bus. The state machine within the bridge will automatically select16 or 32 bit IP width based on the address space utilized. 32 bit accesses to 16 bit ports will be converted to double accesses. 32 bit accesses to 32 bit ports will be handled in a single access. The Byte Swap [BS], Word Swap [WS], Address Increment, and Word High allow the accesses to be customized for the IP installed for optimum performance. 32 bit accesses to 16 bit ports are faster than individual 16 bit accesses and frequently easier to write software for. For example if your IP has a 24 bit port with 16 bits in one register and 8 in the next you can write all 24 with one 32 bit access. With word and byte swapping you can account for the organization of the registers on the IP. Some IPs convert 16 bit accesses to double 8 bit accesses – IP-QuadUART for example. If your IP has 16:8 conversion then you can write 32 bits and get 4 – 8 bit writes to your IP in one access.

Read the IP manual and see what strategy is best to communicate with that card then adapt the settings on the cPCI2IP to optimize your accesses to that IP.

For higher performance and ease of use Dynamic Engineering recommends using our Windows® or Linux drivers. The drivers for the Dynamic Engineering IP carriers take care of the local configuration and provide resources to the overlaying IP drivers. When combined high speed "plug and play" operation results. The carrier level driver comes with a "generic" driver which can be used with any IP and is provided to cover IP's from third parties without a board specific driver. Please contact Dynamic Engineering to write a driver for your IP.

## **Register Definitions**

## cPCl2IP\_intreg\_base

[\$00 Main Control Register Port read/write]

| CONTROL REGISTER 0 |                                        |  |  |

|--------------------|----------------------------------------|--|--|

| DATA BIT           | DESCRIPTION                            |  |  |

| 31                 | Reset 1 = reset IPs 0 = normal         |  |  |

| 30-14              | spare                                  |  |  |

| 13                 | INT FORCE 1 = FORCE 0 = NORMAL         |  |  |

| 12                 | Master INT EN 1 = ENABLED 0 = DISABLED |  |  |

| 11                 | spare                                  |  |  |

| 10                 | spare                                  |  |  |

| 9                  | Bus Error Int/Status Clear             |  |  |

| 8                  | Bus Error Int En                       |  |  |

| 7                  | LED7 1 = ON 0 = OFF                    |  |  |

| 6                  | LED6                                   |  |  |

| 5                  | LED5                                   |  |  |

| 4                  | LED4                                   |  |  |

| 3                  | LED3                                   |  |  |

| 2                  | LED2                                   |  |  |

| 1                  | LED1                                   |  |  |

| 0                  | LED0                                   |  |  |

|                    |                                        |  |  |

FIGURE 5 CPCI2IP CONTROL PORT

Reset when set causes a reset to the IP slots. Reset is active as long as the Reset signal is asserted.

LED7-0 are the user LEDs situated at the right side of the card near Slot B. Each LED can be activated by setting the corresponding data bit and deactivated by clearing the same bit. The LEDs are aligned 0x12 would be

off

off

off

on off

off

on

off

Spare means undefined.

INT FORCE will, when set, cause INTA on the PCI bus to be asserted. This bit can be useful for software debugging. Set this to simulate an IP interrupt when the hardware is not available. The master interrupt must be enabled to have an effect.

Master Interrupt Enable must be set to allow the IP or other interrupt conditions to become an interrupt on the PCI bus. 1 = enabled. 0 = disabled or masked.

Bus Error Int En when '1' allows the bus error detection circuit to cause an interrupt to the host when a Bus Error is detected. The status is available on the Interrupt status register. When '0' the status is still valid but no interrupt is generated when a bus error is detected. The bus error is detected when an access to one of the 5 IP slots is not responded to by IP hardware within the time-out period of approximately 7.3 uS. The bus error circuit is always enabled and automatically responds as if the IP had responded. The data read will typically be \$FF if the IP is not driving the bus for a bus error read. For a bus error write the write should be assumed to not have taken place. The host will not know that the bus error has taken place unless the host checks the status. The interrupt can provide a prompt to check the status during operation. During initialization if the software is checking to "see" what is installed or what address range is valid on an IP then the status can be polled to see if the IP responded.

Bus Error Status / INT Clear when '1' will clear the status bit and interrupt request [if enabled]. The Clear bit needs to be reset to '0' to be able to capture the next Bus Error. The bus error timer hardware operates independent of clearing the status and will continue to monitor and intercede whether the status is read or cleared.

#### cPCI2IP\_intreg\_(a-b)

[\$2000,3000 Slot Control Register Port read/write]

| Slot CONTROL REGISTER (A-E) |                                     |  |  |

|-----------------------------|-------------------------------------|--|--|

| DATA BIT                    | DESCRIPTION                         |  |  |

| 31-9                        | Undefined                           |  |  |

| 8                           | bus error status/clear              |  |  |

| 7                           | word swap control                   |  |  |

| 6                           | byte swap control                   |  |  |

| 5                           | Interrupt Enable 1                  |  |  |

| 4                           | Interrupt Enable 0                  |  |  |

| 3                           | High Word Access                    |  |  |

| 2                           | Increment Disable                   |  |  |

| 1                           | spare                               |  |  |

| 0                           | Speed Control 1 = 32 MHz, 0 = 8 Mhz |  |  |

|                             |                                     |  |  |

FIGURE 6

CPCI2IP SLOT CONTROL PORT

**Speed Control** selects the slot clock speed. 1 = 32 MHz. 0 = 8 MHz. Clock selection change can be made at any time. Each slot has a separate speed control bit. Default is 8 MHz.

**Increment Disable**, when '1', turns off the address increment that normally occurs between 16-bit IP cycles when a 32-bit PCI access is performed. This is useful if, for instance, a FIFO is mapped to a single IP address since it allows double IP accesses to the same address with a single PCI transfer. All types of access are affected (i.e. MEM, IO, INT, and ID). Each slot has independent controls and operation. Only 32 bit accesses are affected.

**High Word Access** controls which 16-bit word is accessed when the Increment Disable is asserted. When '0' the lower word is accessed twice, when '1' the upper word is accessed twice. This bit only has an effect when the Increment Disable bit is '1'. For correct functioning, please make sure the PCI access is on a long-word boundary.

**Interrupt Enable** 0,1 individual masks for the 2 interrupts from each of the provided slots. 0 corresponds to INT0 and 1 corresponds to INT1.

**Byte Swap** when '1' causes the byte lanes to be swapped. For a 16-bit access the upper byte is swapped with the lower byte. For a 32-bit access to a 16-bit port the upper and lower of each word are swapped. For a 32-bit access to a 32-bit port the

bytes and words are swapped so D31-24 becomes D7-0 etc. Byte Swap when '0' provides the data on the same byte lanes that the PCI bus provides them on. Byte Swapping can be used in conjunction with the Word Swap feature for big endian  $\Leftrightarrow$  little endian conversion.

#### 16 bit ports

D15-8 ⇔ D7-0 D31-24 ⇔ D23-16

FIGURE 7

**CPCI2IP 16 BIT BYTE SWAPPING**

#### 32 bit ports

D31-24 ⇔ D7-0 D23-16 ⇔ D15-8 D15-8 ⇔ D23-16 D7-0 ⇔ D31-24

**Word Swap** when '1' will cause the upper and lower words to be swapped. Data written to PCI D15-0 will be driven onto the IP bus as if it originated on D31-16. Word Swap when '0' leaves the data on the PCI word definitions. Please note that Word Swap has no effect on 32 bit accesses to 32 bit IP Module ports.

The IP bus interface state-machine will move data from D15-0 to the "0" address and from PCI D31-16 to the IP "2" address. IP addresses are word based for non-32 bit capable accesses [even with 32 bit transfers]. The PCI bus will write data to either the upper or lower words and apply the corresponding CBE byte lane strobes. The cPCI2IP hardware will translate the data to D15-0 on the IP.

Word swapping can be used effectively for big endian ⇔ little endian translation and to accommodate IPs with registers that can be more effectively accessed in reverse order. For example: if the IP registers are organized with the MS data at address 0x00 and the LS data at 0x02 then a single 32 bit write can be made to 0x00 with address incrementing enabled and word swapping enabled so that the PCI D31-16 data is written to IP 0x00 and the PCI D15-0 data is written to IP 0x02. If the IP registers have data 16 bits or less then word swapping will not be needed.

With the combination of Byte and Word Swapping plus address definition any byte/word can be direct to/from any destination. Big  $\Leftrightarrow$  little endian issues can be resolved and IP architecture optimized for software access.

The **bus erro**r bit is a status bit with a write clear. The clear is active at the time of the write only and does not need to be reset. If the bus error bit is set when the register is read then a bus error has occurred on this slot. Once set the bit will remain set until explicitly cleared by writing a '1' to this bit position.

## cPCl2IP\_intreg\_int

[\$7000 CPCI2IP interrupt register read only]

| CONTROL REGISTER 0 |                                 |  |  |

|--------------------|---------------------------------|--|--|

| DATA BIT           | DESCRIPTION                     |  |  |

| 31                 | IntForce                        |  |  |

| 30                 | <b>'</b> 0'                     |  |  |

| 29                 | Bus Error Slot AB               |  |  |

| 28                 | <b>'</b> 0'                     |  |  |

| 27                 | <b>'</b> 0'                     |  |  |

| 26                 | Bus Error Slot B                |  |  |

| 25                 | Bus Error Slot A                |  |  |

| 24                 | <b>'</b> 0'                     |  |  |

| 23                 | <b>'</b> 0'                     |  |  |

| 22                 | Bus Error 1= occurred 0 = none  |  |  |

| 21                 | <b>'</b> 0'                     |  |  |

| 20                 | <b>'</b> 0'                     |  |  |

| 19                 | <b>'</b> 0'                     |  |  |

| 18                 | <b>'</b> 0'                     |  |  |

| 17                 | <b>'</b> 0'                     |  |  |

| 16                 | <b>'</b> 0'                     |  |  |

| 15                 | UNMASKED B1                     |  |  |

| 14                 | UNMASKED B0                     |  |  |

| 13                 | UNMASKED A1                     |  |  |

| 12                 | UNMASKED A0 1 = SET 0 = NOT SET |  |  |

| 11                 | <b>'</b> 0'                     |  |  |

| 10                 | INTRN 1 = SET, 0 = NOT SET      |  |  |

| 9                  | ·0·                             |  |  |

| 8                  | ΄Ο΄                             |  |  |

| 7                  | ·0·                             |  |  |

| 6                  | ΄Ο΄                             |  |  |

| 5                  | ·0·                             |  |  |

| 4                  | ·0'                             |  |  |

| 3                  | MASKED B1                       |  |  |

| 2                  | MASKED B0                       |  |  |

| 1                  | MASKED A1                       |  |  |

| 0                  | MASKED A0 1 = SET 0 = NOT SET   |  |  |

|                    |                                 |  |  |

#### FIGURE 9

#### CPCI2IP INTERRUPT STATUS PORT

The interrupt requests from each of the IP slots are available as status from this port. The interrupt requests are inverted to make them active high for software usability. The requests are available in a masked and unmasked form to allow polling with the PCI interrupt masked off. When an interrupt is detected this register should be accessed to determine the source or sources and then appropriate action taken to clear the interrupt

at the IP or clear the mask on cPCl2IP.

The cPCI2IP provides direct access to the interrupt space. If the IP causing the interrupt requires an interrupt vector fetch to clear the interrupt then the appropriate INT space should be accessed. Address bit A1 selects between Int0 and Int1. A1 follows the word address to allow access to both INT0 and INT1 clearing addresses within the INT space.

If the IP does not require a Vector fetch then proceed with IO or other accesses as necessary.

The Bus Error status bit is set high when a Bus Error is handled by the internal watch dog timer circuit. The status will stay high until cleared with the Bus Error Int / Status Clear bit in the base control register. The Bus Error status bit is or'd into the interrupt request logic and if enabled will cause a level sensitive interrupt to the host. The interrupt will remain asserted until the status is cleared. The cPCI2IP Base register contains the enable and clear for the bus error logic.

#### cPCI2IP intreg dswitch

[\$6000 User Switch Port read only]

| DipSwitch Port |                |  |

|----------------|----------------|--|

| DATA BIT       | DESCRIPTION    |  |

| 23-16          | Revision Minor |  |

| 15-8           | Revision Major |  |

| 70             | Sw70           |  |

FIGURE 10

**CPCI2IP USER SWITCH PORT**

The user switch is read through this port. The bits are read as the lowest byte. Access the port as a long word and mask off the undefined bits. Read only. The dip-switch positions are defined in the silkscreen. For example the switch figure below indicates a 0x12.

The FLASH revision is read from this port. The Revision Major field is also mapped to the PCI interface and reported through the configuration space. This field can be read and used as a switch when new features are added to the card. The Minor revision is rolled whenever changes are made no matter how small [and released]. The Major field is updated when larger changes are made.

Current Revision: 7p4

## **Applications Guide**

#### Interfacing

Some general interfacing guidelines are presented below. Do not hesitate to contact the factory if you need more assistance.

**Start-up** Make sure that the "system" can see your hardware before trying to access it. Many BIOS will display the PCI devices found at boot up on a "splash screen" with the VendorID 0x10EE and CardId 0x0011 and an interrupt level. Alternatively in Windows you can use the device manager and in Linux the LSPCI command to see what is installed.

**Watch the system grounds**. All electrically connected equipment should have a fail-safe common ground that is large enough to handle all current loads without affecting noise immunity. Power supplies and power consuming loads should all be connected to a common point.

**Power control and static electricity.** As the internal dimensions of integrated circuits continues to shrink the susceptibility to static damage increases. Treat the cPCI2IP and IP Modules as static sensitive to insure long life within your system.

Consider the power flow within your system and make sure that un-powered equipment will not be subjected "reverse energising" from active signals when the power is off. The easiest way to deal with this is to turn all of the equipment on and off together. When your equipment is part of a larger system that can't be powered down then isolation or IO types that allow for hot connection should be employed on the IPs installed onto the cPCI2IP.

**Connector definition.** cPCI2IP has two IO options. The front panel IO is provided with a "condo" header; two 50 pin ribbon cable connectors stacked. The ribbon cable connectors have ejectors which are handy for retention and cable removal.

The IO can also be accessed via the J2 connector on the cPCI bus. The cPCI specification allows for either 64 bit PCI implementations or user IO on J2. If your cPCI slot has 64 bit PCI data then the non-backplane IO version of the card must be used to avoid conflicts on the bus. With a 32 bit PCI bus the IO can be accessed from the rear or the front panel. The Front panel IO is always installed. When the rear IO is not installed the IO is isolated by removing the J2 connector and not installing the isolation resistors. The isolation resistors are located near the front panel IO to minimize the unused trace length when using the front panel IO. For "safety" the standard version has the front panel IO installed [only]. The –J2 option adds in the J2 connector and

isolation resistors.

Please refer to the connector definition tables for pin-outs. The front panel IO is 1:1 with standard ribbon cable definitions. The rear panel IO [J2] follows the cPCI specification [PICMG® 2.0 R3.0.]

#### **Engineering Kit**

Dynamic Engineering provides Engineering Kits to help our customers have a successful and quick integration. Engineering Kits will save time and money with decreased T&I. We recognize that different customers have different needs. The Engineering Kits are standardized in description to help with selection. The kits are segmented to allow for customers who only need hardware support, software support or a mixture. The Engineering Kit is highly recommended for first time buyers. The kit pricing is discounted to encourage their use.

cPCI2IP-Eng-1 .......... Hardware Support Engineering Kit includes: IP-Debug-Bus, IP-Debug-IO.

cPCI2IP Drivers........ Software Support Windows® and Linux compliant drivers for the cPCI2IP. The driver is designed to be overlayed with individual IP Module(s) driver(s). Please see the Driver manual for the specifics of writing your board interface. Please contact Dynamic Engineering if you would like us to produce one for your IP or a third party design. Currently available drivers for the carrier and are included with the purchase. A reference application and Generic IP driver are also included.

Linux drivers may need adjustment to your particular version of Linux. See SW manual for details of current versions tested against.

## J2 IP Module IO Pin Assignment

| AIO            | J2         | BIO              | J2  |                        |

|----------------|------------|------------------|-----|------------------------|

|                | A11        |                  | A21 |                        |

| 1<br>2<br>3    |            | 1<br>2<br>3      |     |                        |

| 2              | B11        | 2                | B21 |                        |

|                | C11        | 3                | C21 |                        |

| 4              | D11        | 4<br>5<br>6<br>7 | D21 |                        |

| 5              | E11        | 5                | E21 |                        |

| 5<br>6<br>7    | A10        | 6                | A20 |                        |

|                | B10        |                  | B20 |                        |

| 8              | C10        | 8                | C20 |                        |

| 9              | D10        | 9                | D20 |                        |

| 10             | E10        | 10               | E20 |                        |

| 11             | A9         | 11               | A19 |                        |

| 12             | B9         | 12               | B19 |                        |

| 12<br>13       | C9         | 13               | C19 |                        |

| 14             | D9         | 14               | D19 |                        |

| 15             | E9         | 14               | E19 |                        |

| 16             | A8         | 16               | A18 |                        |

| 10             | A0<br>D0   | 16               |     |                        |

| 16<br>17<br>18 | B8         | 17               | B18 |                        |

| 10             | C8         | 18               | C18 |                        |

| 19             | D8         | 19               | D18 |                        |

| 20             | E8         | 20               | E18 |                        |

| 21             | A7         | 21               | A17 |                        |

| 22             | B7         | 22               | B17 |                        |

| 23             | C7         | 23               | C17 |                        |

| 24             | D7         | 24               | D17 |                        |

| 25<br>26       | E7         | 25               | E17 |                        |

| 26             | A6         | 26               | A16 |                        |

| 27             | B6         | 27               | B16 |                        |

| 27<br>28       | C6         | 28               | C16 |                        |

| 29             | D6         | 29               | D16 |                        |

| 30             | E6         | 30               | E16 |                        |

| 31             | A5         | 31               | A15 |                        |

| 32             | B5         | 32               | B15 |                        |

| 33             | C5         | 33               | C15 |                        |

| 24             | D5         | 24               | D15 |                        |

| 34             |            | 34               |     |                        |

| 35             | E5         | 35<br>36         | E15 |                        |

| 36             | A4         | 36               | A14 |                        |

| 37             | B4         | 37<br>38         | B14 |                        |

| 38             | C4         | 38               | C14 |                        |

| 39             | D4         | 39               | D14 |                        |

| 40             | E4         | 40               | E14 |                        |

| 41             | A3         | 41               | A13 |                        |

| 42             | B3         | 42               | B13 |                        |

| 43             | C3         | 43               | C13 |                        |

| 44             | D3         | 44               | D13 |                        |

| 45             | E3         | 45               | E13 |                        |

| 46             | A2         | 46               | A12 |                        |

| 47             | B2         | 47               | B12 |                        |

| 48             | C2         | 48               | C12 |                        |

| 49             | D2         | 49               | D12 |                        |

| 50             | E2         | 50               | E12 |                        |

| FIGURE 11      | L <i>L</i> |                  | L12 | CPCL 12 PIN ASSIGNMENT |

FIGURE 11 CPCI J2 PIN ASSIGNMENT Additional J2 pins: A1,B1,C1 = 3.3V D1,E1 = 5V, F1-22 = GND PICMG® 2.0 R 3.0 compliant.

## **Construction and Reliability**

IP Modules were conceived and engineered for rugged industrial environments. The cPCI2IP is constructed out of 0.062 inch thick high temperature RoHS compatible FR4 material.

Through hole and surface mounting of components are used. High insertion and removal forces are required, which assists in the retention of components. If the application requires unusually high reliability or is in an environment subject to high vibration, the user may solder the corner pins of each socketed IC into the socket, using a grounded soldering iron.

The IP Module connectors are keyed and shrouded with Gold plated pins on both plugs and receptacles. They are rated at 1 Amps per pin, 200 insertion cycles minimum. These connectors make consistent, correct insertion easy and reliable.

The IP Module can be secured against the carrier with the connectors. If more security against vibration is required then IP mounting kit can be used to attach the IP to the carrier. Dynamic Engineering has mounting kits available if your IP did not come with one.

https://www.dyneng.com/IPHardware.html

#### **MTBF**

cPCI2IP has been modeled with Belcore reliability prediction software. The MTBF is reported as greater than 1,290,549 Hrs. GB 25C.

#### **Thermal Considerations**

The cPCI2IP design consists of CMOS circuits. The power dissipation due to internal circuitry is very low. The installed IP Modules may require forced air cooling. With the one degree differential temperature to the solder side of the board external cooling is easily accomplished.

## **Warranty and Repair**

Please refer to the warranty page on our website for the current warranty offered and options.

https://www.dyneng.com/warranty.html

#### Software

Is included and delivered "AS-IS" Integration support packages are available to help your project. <a href="https://www.dyneng.com/TechnicalSupportFromDE.pdf">https://www.dyneng.com/TechnicalSupportFromDE.pdf</a> is a link to the details.

## **Extended Warranty**

The hardware warranty period can be extended by up to 2 additional years, providing a 3 year hardware warranty. The extended warranty fee is 5% of the current list price of the hardware per year purchased. The extended warranty can be purchased for either 1 or 2 additional years. The extended warranty must be purchased at the time of original hardware purchase. The extended warranty covers labor and readily available, off the shelf components, the extended warranty does not cover obsolete or special order components.

#### **Service Policy**

Before returning a product for repair, verify as well as possible that the suspected unit is at fault. Then call the Customer Service Department for a RETURN MATERIAL AUTHORIZATION (RMA) number. Carefully package the unit, in the original shipping carton if this is available, and ship prepaid and insured with the RMA number clearly written on the outside of the package. Include a return address and the telephone number of a technical contact. For out-of-warranty repairs, a purchase order for repair charges must accompany the return. Dynamic Engineering will not be responsible for damages due to improper packaging of returned items. For service on Dynamic Engineering Products not purchased directly from Dynamic Engineering contact your reseller. Products returned to Dynamic Engineering for repair by other than the original customer will be treated as out-of-warranty.

#### **Out of Warranty Repairs**

Out of warranty repairs will be billed on a material and labor basis. Customer approval will be obtained before repairing any item if the repair charges will exceed one half of the quantity one list price for that unit. Return transportation and insurance will be billed as part of the repair and is in addition to the minimum charge.

#### For Service Contact:

Customer Service Department Dynamic Engineering 150 DuBois St. Suite B&C Santa Cruz, CA 95060 831-457-8891 support@dyneng.com

## **Specifications**

Logic Interfaces: IP Logic Interface, PCI Interface -33 MHz. 32 bit, universal signaling

Access types: IO, ID, MEM, INT IP Spaces supported via cPCI bus accesses

CLK rates supported: 8 MHz or 32 MHz slot by slot selectable

33 MHz. cPCI

Software Interface: Control Registers, and Installed IP. Programming procedure documented in this

manual

Access Modes: LW, Word or Byte to IP registers LW can be converted to two word accesses or

as a LW to a 32 bit IP. LW to Internal PCI Interface Control registers. Bus error

detection and handling.

Access Time: Typical access time with 32 MHz. IP and double access mode is 500 nS.

Interrupt: 2 Interrupts per IP slot with separate enables., Programmable Bus error interrupt

DMA: No DMA Support implemented at this time

Onboard Options: All Options are Software Programmable

Interface: 50 pin Header Connectors

Dimensions: 3U 4HP

Construction: FR4 Multi-Layer Printed Circuit, Through Hole and Surface Mount Components.

Programmable parts are socketed.

Power: RF filtered and fused to each IP slot. Re-settable "self healing" fuses.

User 8 position software readable switch

8 software controllable LEDs

Other LED LEDs (3) on slot B power (±12,5) LEDs (2) used to show IP

acknowledge to access - 1 per slot.

Slots 2 single wide IP slots with double wide and 32 bit capability in slot pairs

A/B

Temperature Range -40 ⇔ +85C for carrier components. IP temperature range will affect

assembly range.

Temperature Coefficient: 2.17 W/OC for uniform heat across Carrier

MTBF 1,290,549 Hrs. GB 25C

## **Order Information**

Industrial temperature range -40-85°C

cPCI2IP <a href="https://www.dyneng.com/cpci2ip.html">https://www.dyneng.com/cpci2ip.html</a>

3U cPCI card with 2 IP positions, front panel IO only

cPCI2IP-J2 <a href="https://www.dyneng.com/cpci2ip.html">https://www.dyneng.com/cpci2ip.html</a>

3U cPCI card with 2 IP positions, J2 IO only

cPCI2IP-IO <a href="https://www.dyneng.com/cpci2ip.html">https://www.dyneng.com/cpci2ip.html</a>

3U cPCI card with 2 IP positions, front panel IO and J2 IO

cPCI2IP-ET-J2 https://www.dyneng.com/cpci2ip.html

3U cPCI card with 2 IP positions, J2 IO only

cPCI2IP-ET-IO <a href="https://www.dyneng.com/cpci2ip.html">https://www.dyneng.com/cpci2ip.html</a>

3U cPCI card with 2 IP positions, front panel IO and J2 IO

IP-DEBUG-BUS https://www.dyneng.com/ipdbgbus.html

IP test points, reset switch, fused power, quick switch isolated

interface lines to allow hot swapping of IP cards.

IP-DEBUG-IO https://www.dyneng.com/ipdbgio.html

Isolate the IO connector to help with debugging. 50-pin header for system cable connection. 50 testpoints suitable for wire-wrap to allow loop-back connections. Locations for power and user

circuits.

HDRterm50 https://www.dyneng.com/HDRterm50.html

50-pin header to 50 screw terminal converter with DIN rail

mounting.

All information provided is Copyright Dynamic Engineering

FIGURE 12

#### **CPCI2IP CONNECTOR REFERENCE**

cPCI2IP has 2 slots (A,B) and 2 header connectors associated with those slots. J3 is a stacked – dual header connector with ejectors and keying. A and B are marked on the bezel.

The wiring is 1:1 from the IP IO connector to the cPCI2IP header connector. The connectors are numbered to match standard ribbon cable as shown in the figure to the right.

The J2 connector can be installed when the cPCI backplane has IO defined on J2. The IO is isolated with series